|

Ҫ��Ƴ��ߴ��С�ĵ��������������ڶ��������ӡˢ��·�� (PCB) �в��ø��ܶ���ƣ�����ÿ���ʹ���ʡ��ڶ���װ�����·�����ƺ���������У��������ò��ɻ�ȱ��������Ҫʹ�ù����ƹ�����ʵ�ִ�һ�㵽��һ��IJ��ߡ���ȻҲ����ʹ��ͨ��ä�ף��������ֿ�ռ���˹���Ŀռ䣬ʹ�ø��Ӻ��ܶȵ����������Բ��ߡ�Ҫ���������⣬����ʹ���ѵ��Ĺ��ף����������������ϵķֲ���ױ˴˶ѵ���һ����

Allegro Package Designer Plus �ṩ��һ��ȫ��Ĺ��ܣ�����������ɸ��ܶȸ��ӵķ�װ��������棬���ǽ����� Allegro Package Designer Plus ���ߣ�̽������ڸ��ܶȸ��ӵķ�װ�����ʹ�÷�Բ�εĶѵ����ס�

01. / / �������ݿ�

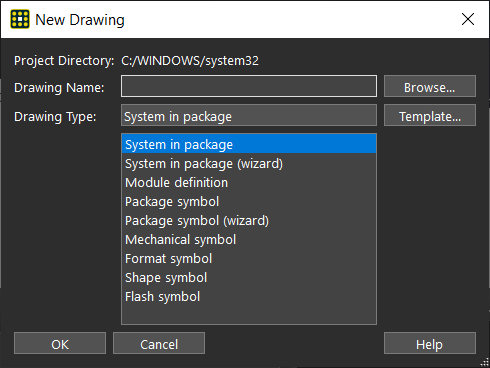

Ҫ�봴����Բ�εĶѵ����ף�����Ҫ����һ�����ݿ⡣���� Allegro Package Designer Plus��ʹ�� File �C New ���ܴ���һ���µ�ͼ����Ȼ�档

02. / / ����

����һ���У�ʹ�� File �C Import �˵��е� Techfile �� Parameter ѡ������ѵ������ļ��Ͳ����ļ���ѡ�� Setup �C Cross-section���� Cross-section Editor ���鿴�ֲ�IJ��档

03. / / ����ͼ������

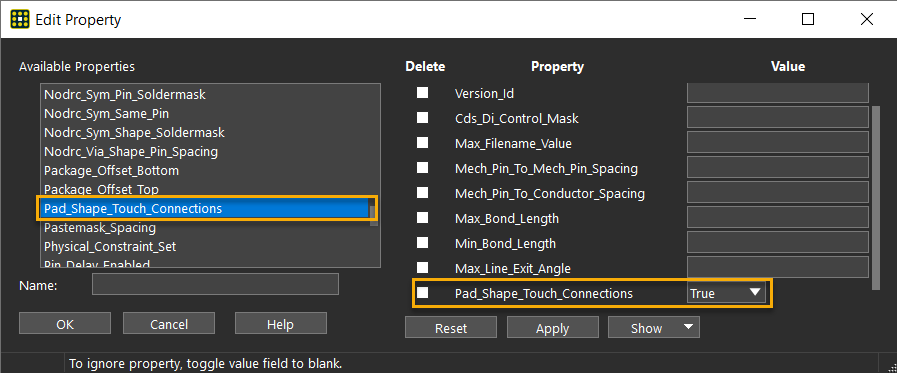

ѡ�� Edit �C Properties���� Find �������н� Find By Name �ֶ�����Ϊ Drawing���� Edit Property �Ի����У��� Pad_Shape_Touch_Connections ��������Ϊ True��Ȼ���� OK��

ע�⣺��ʱ������ѡ�� File �C Save ������ơ�

04. / / ������״����

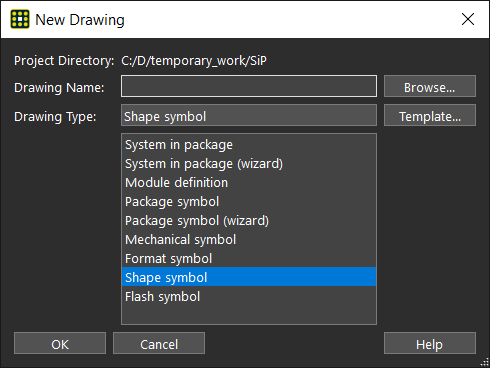

�� Allegro Package Designer Plus �п������ɴ����µ���״��Ϊ�ˣ�ֻ��ѡ�� File �C New��ָ��ͼֽ�����ƣ�ѡ�� Shape Symbol��Ȼ���� OK��

�Ŵ���ʾ����λ�á�ѡ�� Add �C Frectangle���ڻ����ϻ���һ��ʵ�ľ��Σ����� TOP �� BOTTOM ������ꡣ����÷��š��� Project Directory �ֶ�����ʾ��λ�ûᴴ��һ���µ� .dra �ļ���

05. / / ���

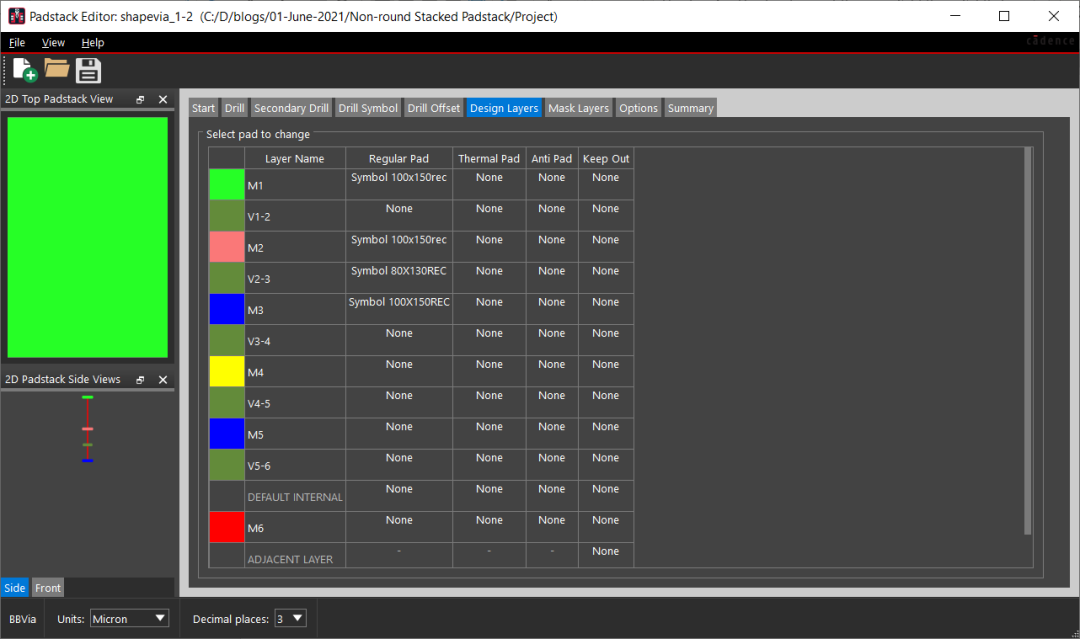

������Բ�ζѵ�������Ҫ�����DZ༭���̣����������ܼ��� .sip �ļ���ѡ�� Tools �C Padstack �C Modify Design Padstack���� Options ѡ���ѡ����״��Ȼ���� Edit��Padstack Editor �漴���� Start ѡ���ѡ�� BBVia��Ȼ���Բ�ͬ�����Ʊ���ú��̡�

�� Design Layers ѡ��£��� Regular Pad ���и��ĸ���Ķ��壬����ͼ��ʾ��Ȼ�溸�̡�

06. / / �ڷŹ���

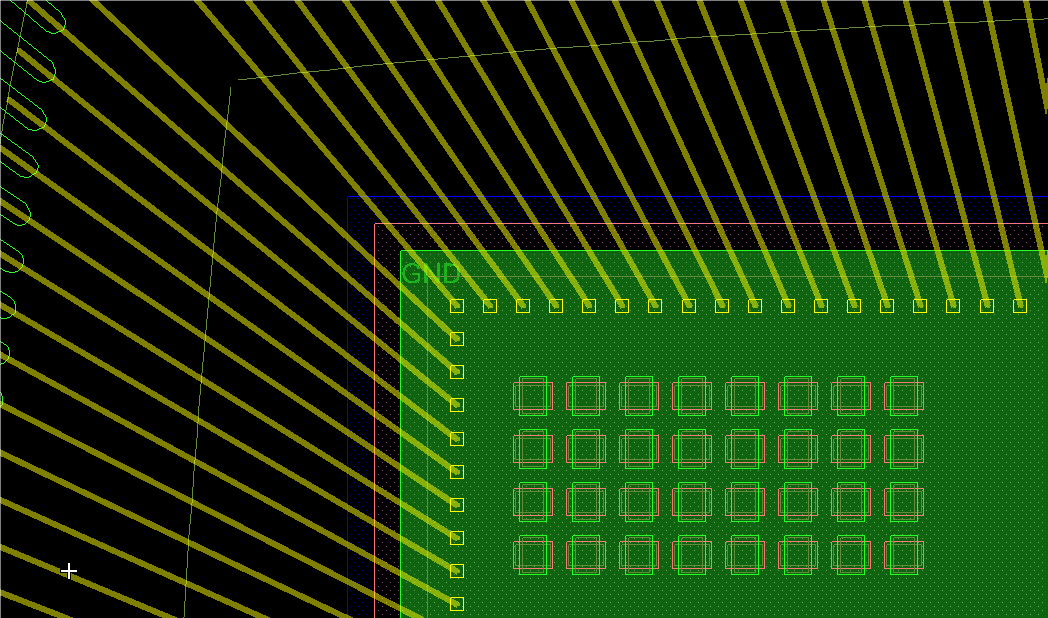

ʹ�÷�Բ�ζѵ��������һ�����ڷ�װ���аڷź���ת���ס�

Allegro Package Designer Plus ������ЩӦ���أ�

�г���Ҫ��Ʒ�ṩ����ܣ��ڴ��ƶ��£����̷�ѡ���Ƚ���װ����Ӧ���ӵ���ơ�Ϊ����Ч�������Щ���ӵķ�װ����Ҫһ�������ʵ�ֹ������������������������Լ����Cadence Allegro® ƽ̨Ϊ PCB ���ӷ�װ����ƺ�ʵ���ṩ������������չ�ļ�����

�������ֹ���

1��Լ����������������

Allegro Package Designer Plus �ṩ�����Ƚ���װ��������ȫ�����ܡ�������������ƹ����� (DRC) ֧�ֲ�ѹ�塢�մɺ���弼���ĸ��ӡ�����Ҫ��֧�ֶ�ǻ�塢������״�Լ�����ʽ���Զ������ϡ�

���̹�������Flow Manager������ʹ�ã��������û����ÿ�������Զ����� IC ��װ��������������ʹ�����Ƭ����װ�����ߡ�������ͻ�ʴ�̡�֧�ֵ����Ͷ����Ƭ����Ƭ�ѵ���˫����Ƭ��ʹ����Ƭ�ͻ������û���������ѡ�� ASCII ����ʽ��Die Text��DEF��AIF������ƬժҪ������������û����棨�硱text in���������Զ�������Щ��Ԫ�ء�

2�����ӵĻ��彨ģ������

���Ը���һ�������������͵�����ƹ���Լ������֤��Ƶ�ȷ�ԡ�����Լ�������û�����ļ����ļ����ƶ����������������ȷ����ƵĿ������ԡ�����Լ�����ź��ӳ١�ʱ��ؼ������ʧ��淶��DesignTrue ����������Ƽ��ּ��ȷ����Ʒ��������̵�Ҫ����������ƹ����У��û����Ը�����ЩԼ����������ƽ��ж�̬��飬ȷ����Ʒ�������͵����淶���û�����ͨ����ƹ��������Լ��ڻ��ڵ��ӱ����Լ���������б��Υ����Ϊ�õ���ʱ������

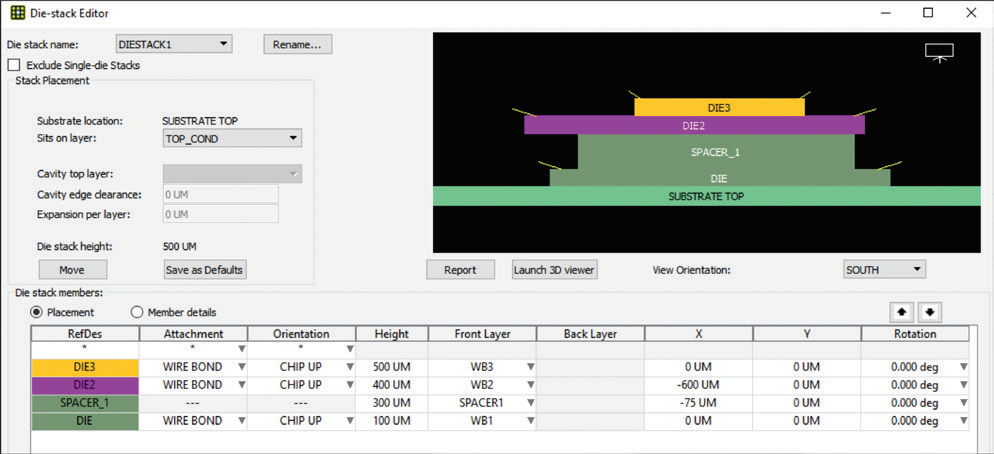

Die Stack Editor�����ڹ������ӵĶ�ջ-��Ƭ�ṹ����������������㡣��Ƭ�����߾������ӡ�

3�����ռ����ظ�ʹ��

����ѵ���Լ����Ϣ����¼�ڼ����ļ��У������ظ������������ƽṹ����ƣ���һ������δ����Ƶ����ڡ��������Dz�����ƻ���������ơ����幩Ӧ�̿����ṩ�����ؼ���ƹ���ļ����ļ����Ա�ʹ����ȷ����Ʒ����������̿��������Լ���Ļ����ϵ������ǵ���װ������Ҫ��֧��ʹ�ò�ͬ��Ӧ�̵Ķ�������ļ���ȷ��������Ӧ�̵Ŀ�������

4�����ܻ������

��ʹ�ÿɲ��ߵ��л������ϸ��൹װоƬ������ IC ��װ����У����ܻ�����HDI��/���㼼����Ӧ�÷dz��ձ顣Allegro Package Designer Plus �ṩȫ���Լ������ HDI ��ƹ��ܣ������ӵ��Զ��������Ľ�����ơ����ӵ��༭���ܵ�ȫ����������������ʦ�ܹ���������Ҫ��ʵ��Ԥ�ڵ���ƺ�������Ŀ�꣨����ͼ����

Լ�������� HDI ����������ʦ����ʵ�ֲ������ظ��ĸ��ӹ��ṹ����������·�����ף����������ݺͲ���ɡ�

5��PCB ϵͳ������

Allegro Package Designer Plus �����ֺ��˹�Ƭ�ͷ�װ���֮��IJ�࣬���һ�����װ�� PCB ����ν�������PCB ����ͼ�滮�Ͳ������������������ݶ������Զ����ɡ������� footprint��ԭ��ͼ���ź�����ģ�͡�����������ţ���Ƭ�� BGA�����������ڵ��ӱ����ж�ȡ����������Щ���ܣ�ϵͳ���ʦ���Խ�ʡ����ʱ�䲢������ݵ�ȷ�ԡ�

Cadence��װ��Ƽ����ܹ���Ч������ҿɿ���ʵ���ܼ����Ƚ���װ��ƣ�����ȫ���ڶ�ͻ������������ɵ��źź͵�Դ�����Է���ȷ������������������ڿ���һ�����������������ս��ʹ�� Cadence ���ɵ�·��װ��Ƽ��������ʦ��������������ŵĹ���Ҫ��ȷ�����һ�γɹ���

��������˽�������Allegro Package Designer Plus ����Ϣ����ӭ��������ϵ~

��������������Cadence

|