|

GDDR 是一种不断发展的接口,适用于许多电子应用。Cadence 利用一整套 EDA 工具包括Cadence Sigrity™ X SI/PI 技术、 Cadence Clarity™ 3D Solver 电磁(EM)仿真器和 Cadence Celsius™ Thermal Solver ,用于根据联合电子器件工程委员会(JEDEC)规范进行仿真和签核,从而以更合理的成本实现 GDDR6,并达到行业标准要求。

之前我们从GDDR6 设计中需要考虑的关键问题、设计同步分析、GDDR6 存储器接口的 SI 仿真平台、创建并行总线拓扑结构几个方面介绍了如何在 GDDR6 接口设计中克服信号、电源和散热挑战,本期我们将详细为大家介绍GDDR6 接口设计的工作流程步骤以及GDDR6 存储器接口的 PI 仿真平台。

■ 工作流程步骤

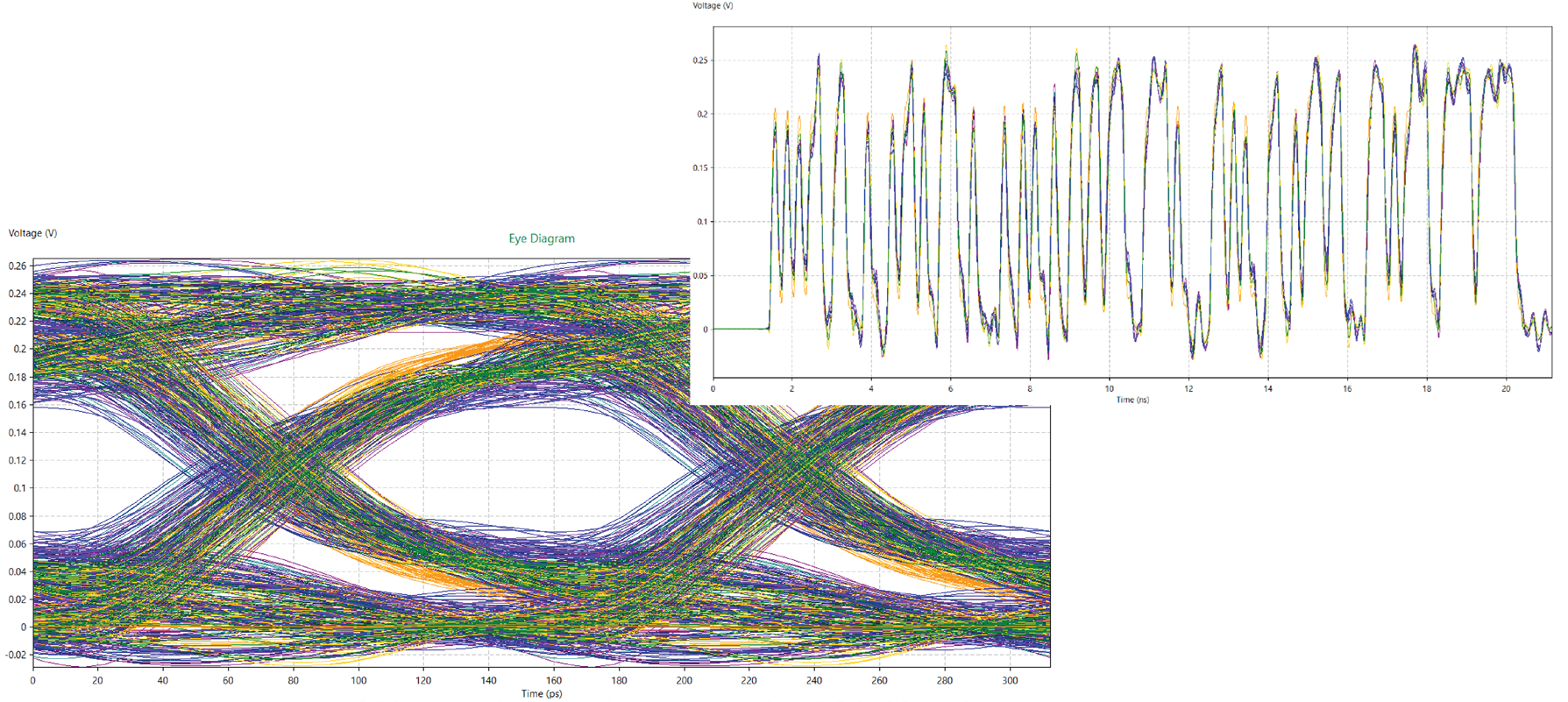

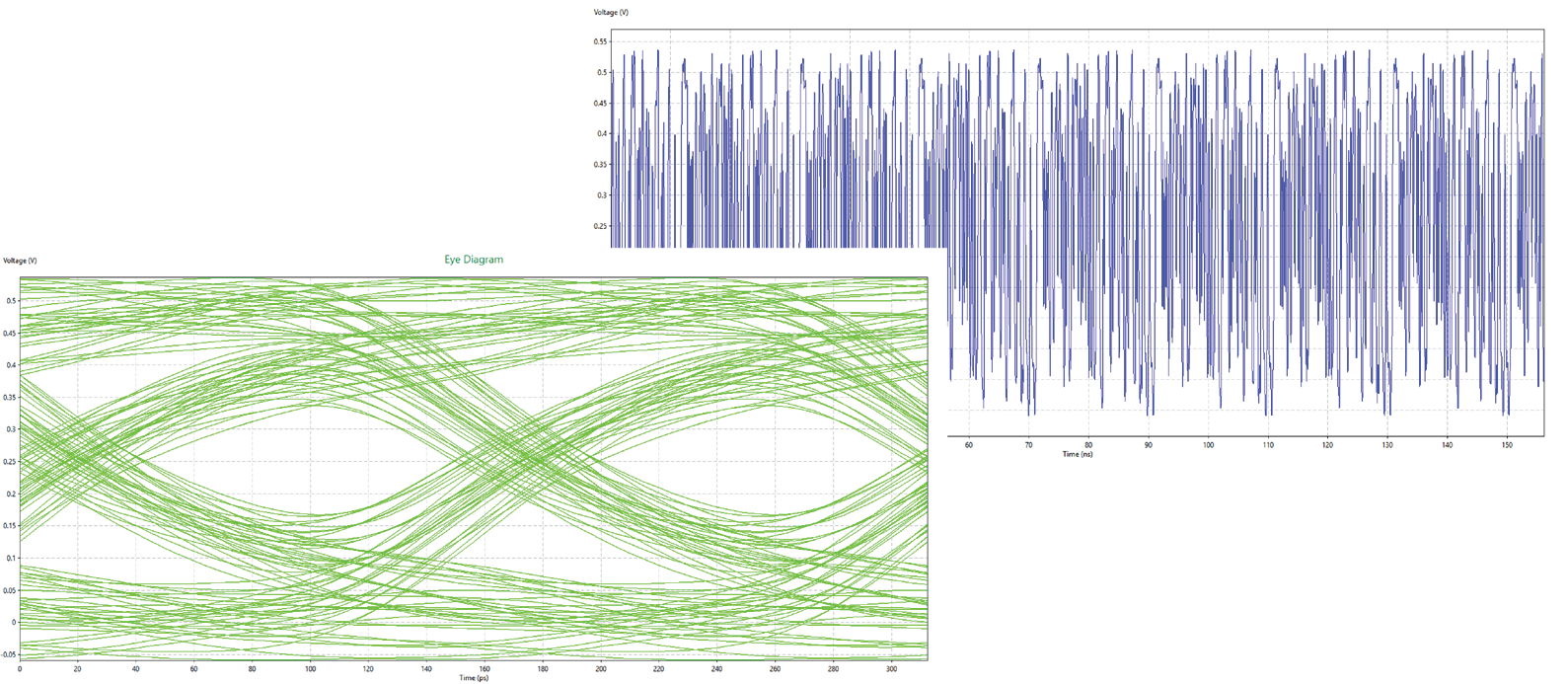

工作流程中的第一步是运行电路仿真来检查波形质量,并确保眼图没有问题(图 6)。

图 6:工作流程的第一步是检查波形质量和眼图

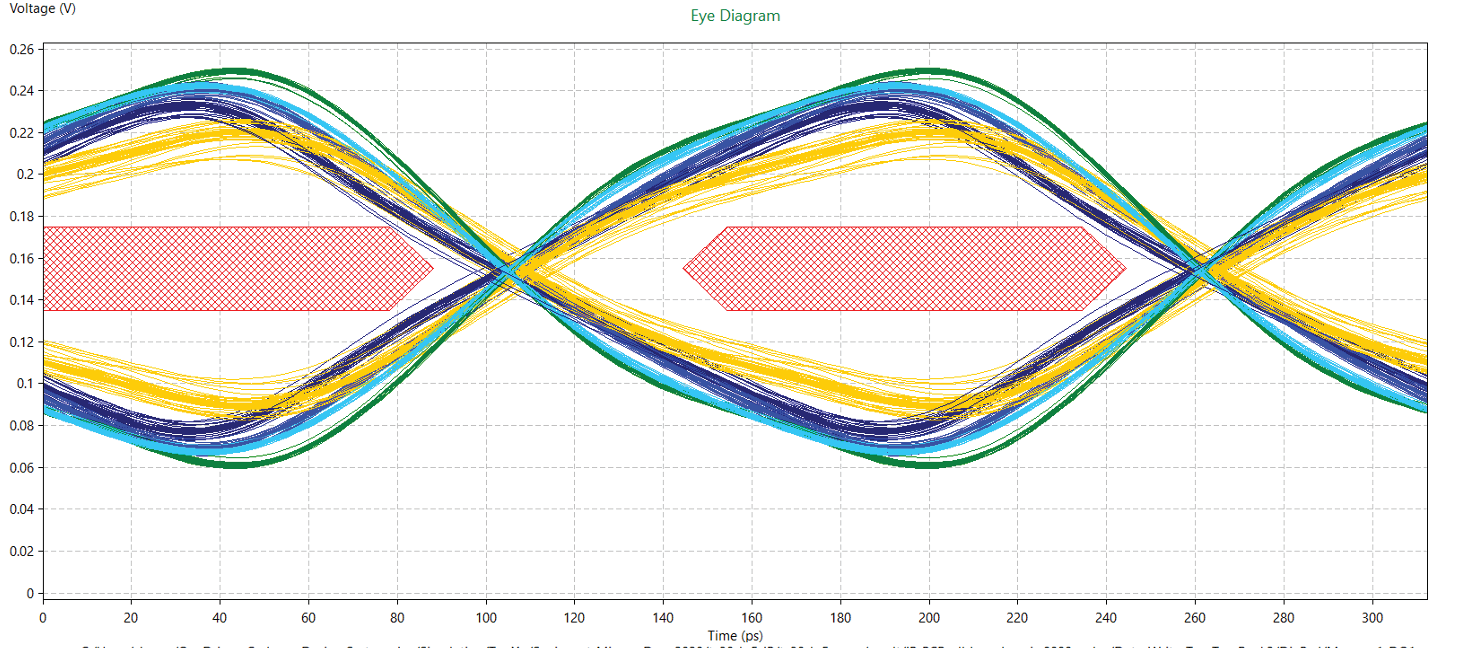

设计者可以检查电路仿真中的总线响应,并检查眼图模板以确保适配(图 7)。

图 7:检查以确保眼图模板适配

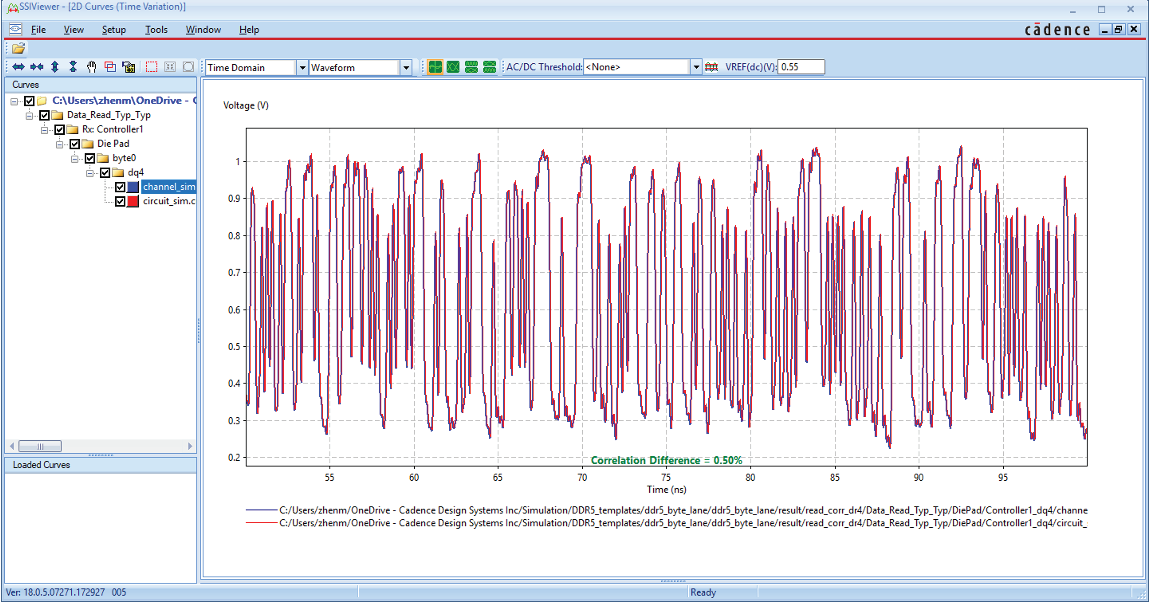

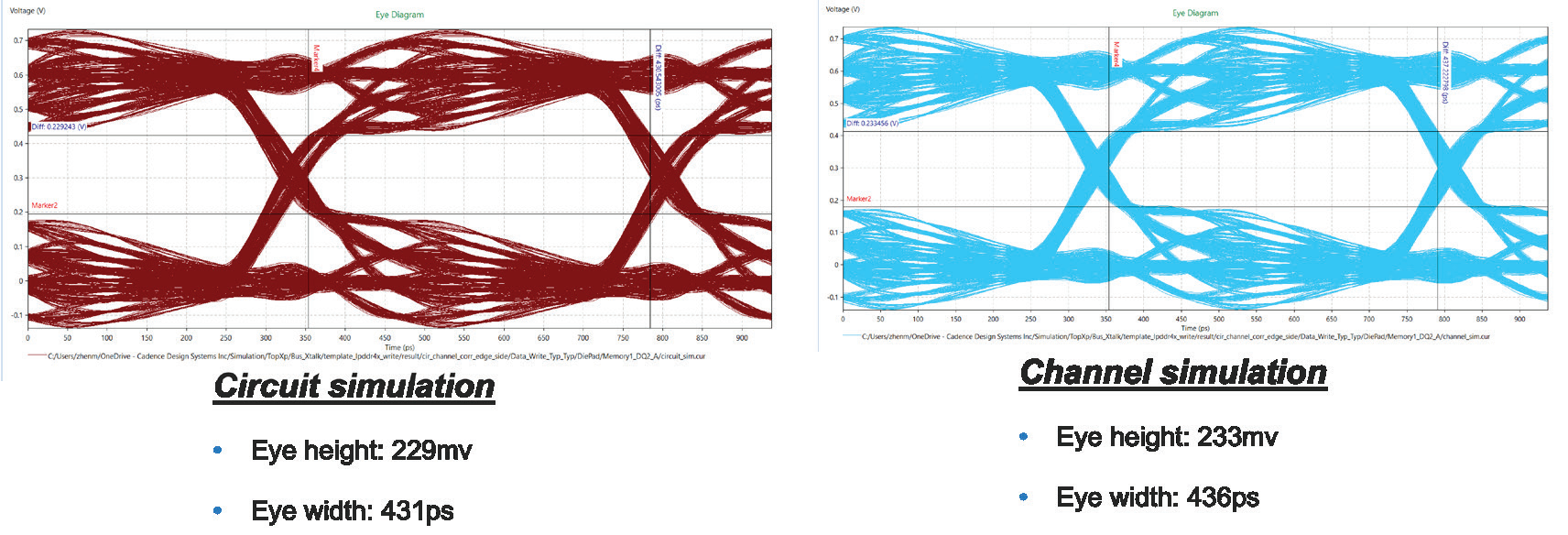

运行初始仿真后,下一步是运行电路/信道相关性。这在该工作流程中也很容易做到,因为工具会自动完成所有的设置和仿真,并提供叠加的视图以作比较(图 8)。

图 8:工作流程中的电路/信道相关性仿真

需要 3% 或更高的匹配度来限定信道仿真的使用,并进入下一步,因为最终将运行数百万比特的信道仿真,来看是否符合用于误码率眼图模板和眼开度的 GDDR6 规范。选择不同的斜坡响应选项,将使 SI 工程师能够找到在容差范围内实现相关性的较佳选项。

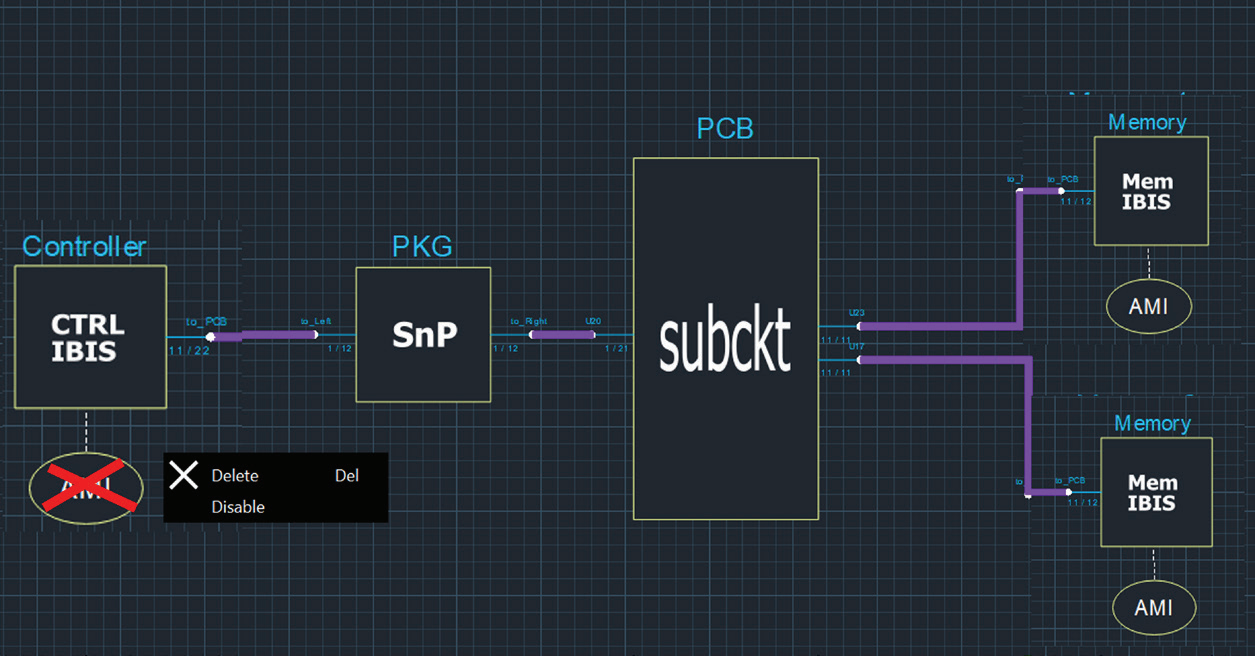

接下来,运行信道仿真,检查 AMI 模型各项配置,确定是否需要启用均衡设置。该工具可以禁用任何 AMI 模型,并运行基线仿真,确定是否需要对控制器、存储器或两者进行均衡(图 9)

图 9:信道仿真和 AMI 模型

确定了均衡需求后,就可以进行假设分析,改变 AMI 参数,并检查其对眼开度的影响或者扫描某些 AMI 参数。可以扫描多个参数,包括AMI 参数。在本例中,对发射和接收的 AMI 参数进行了扫描,每个步骤有三个计数,产生九次迭代。这些结果被叠加,使设计者能够确定给出较佳结果的仿真,并在 AMI 模型中设置这些值。

在确定适当的 AMI 参数后,设计者运行信道仿真来检查波形和眼开度(图 10)。

图 10:波形和眼开的结果

可以指定用于眼图的比特数,默认为保存最后 1000 比特。该工具返回的其他结果包括浴盆曲线和不同信号的眼高报告,以检查更高的误码率导致的眼高减少。

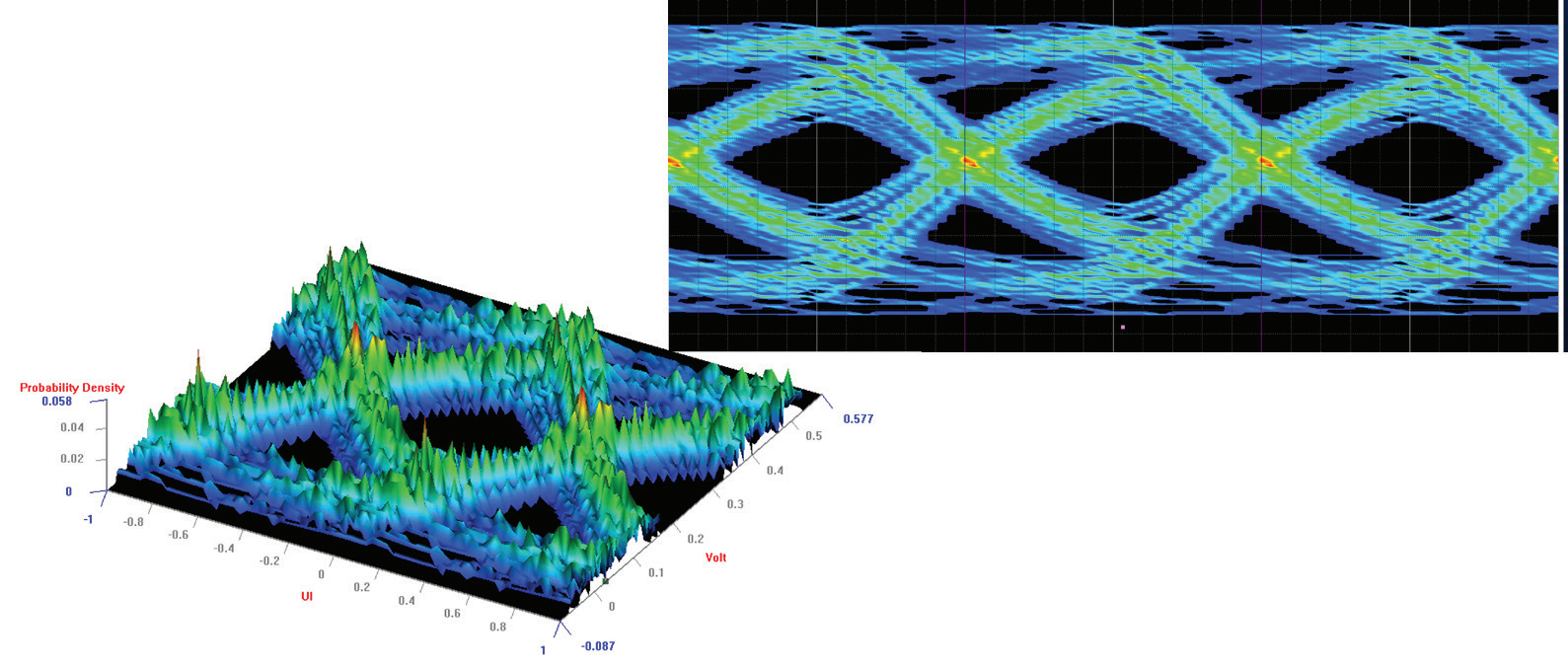

图 11 是一个眼图,显示了 2D 和 3D 视图中噪声和抖动的分布。

图 11:眼图的 2D 和 3D 视图

运行信道仿真后,作为工作流程的一部分,设计者会对总线进行额外的特性分析,以捕获个别信号中的串扰。由于这是信道仿真,所以需要以略微不同于自带的电路仿真的方式对串扰进行特性分析。

图 12 比较了电路仿真和信道仿真下眼图的测量,它们在眼高和眼宽上吻合的很好。这使设计者相信,可以运行一百万比特以上的仿真来捕捉串扰对误码率的影响。这十分重要,有助于了解设计在现场的运行情况并确保满足 GDDR6 合规性要求。

图12 电路仿真(左)和信道仿真(右)的眼图测量结果比较

工作流程的下一步是在信道仿真中包括电源噪声效应。到目前为止,已经假定了控制器和存储器设计的理想电源(VED 和 VCC)。电源噪声的影响需要包括在电路和信道仿真中。信道仿真电源效应是通过表征来捕获的,而电路电源效应是通过互连模型本身来捕获的。

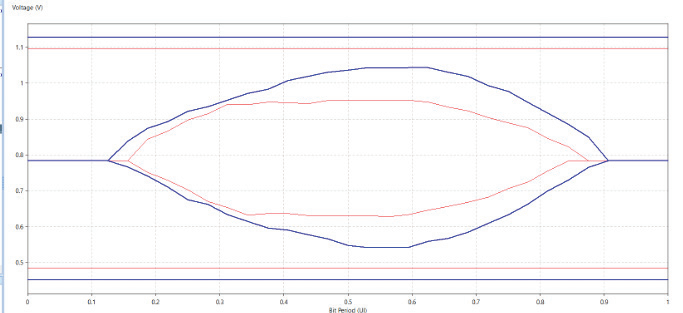

为了验证信道中的电源噪声,要运行两个信道仿真,一个带有理想电源,另一个带有非理想电源。利用仿真结果,设计者可以比较表征响应和其他信道仿真结果,查看非理想电源对眼开度的影响(图 13)。

图 13:表征响应比较,蓝色表示理想电源,红色表示非理想电源和串扰

完成此步骤后,就可以生成一个报告,用于合规性检查和签核。GDDR6 JEDEC 规范被纳入报告生成过程,并包含一个增强的数据速率相关测量结果。该报告强调了任何超标。可以选择报告表中的任何信号,查看 mask 自动计算的眼开。如果存在超标,可以进行假设分析以寻找解决方案。

■ GDDR6 存储器接口的 PI 仿真平台

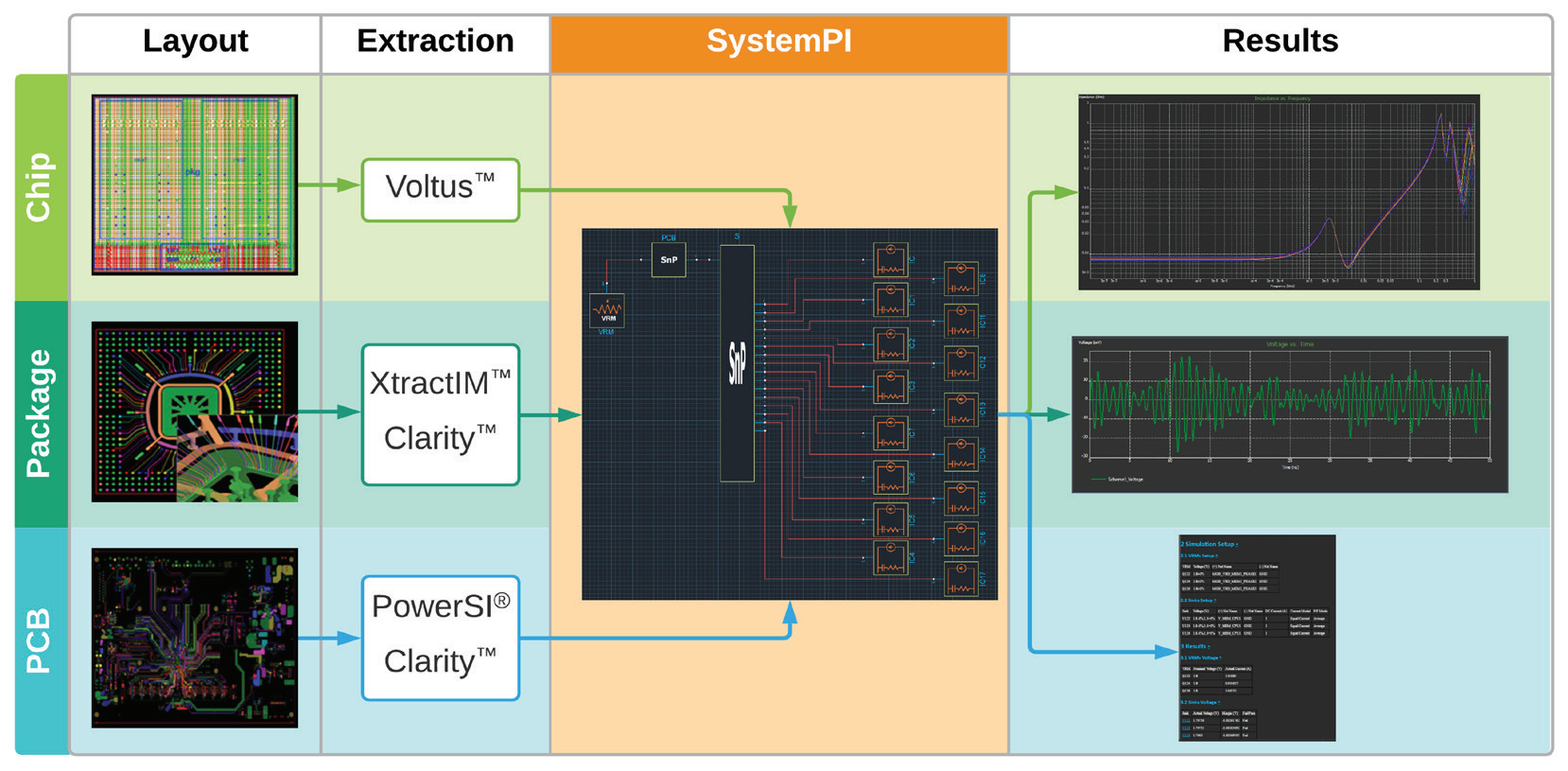

许多信号完整性工程师也负责电源完整性。GDDR6 仿真平台示例也可用于验证 PCB 和 IC 封装流过的足够、有效、稳定和可靠的电源,以实现电源完整性签核(图 14)。

图 14 用于电源完整性分析的 SystemPI 数据流

从信号完整性的角度来看,仿真是从发送器到接收器进行的。对于电源完整性,仿真是从电压源或稳压模块(VRM)到电压sink(器件引脚)进行的。借助基于拓扑结构的新的用户界面,可以方便地通过电缆、连接器和 PCB、封装、中介层等结构连接多个结构。

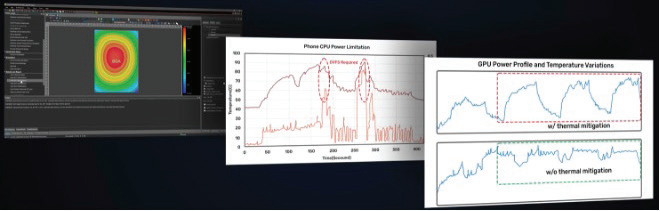

恰当的电源完整性分析必须是兼顾热影响的。压降分析应该与热分析相结合。Cadence Celsius PowerDC™ 和 Celsius Thermal Solver 通过其他 Cadence 分析工具使用的通用用户界面提供电热协同仿真以及 3D 热视图(图 15)。

图 15:Celsius Thermal Solver 检查手机应用中 GPU 的热缓解的情况

■ 结论

存储器接口路线图在不断发展。可能支持 1.5TBps 的 GDDR7 规范正在开发中,美光和 NVIDIA 已经在生产 1TBps 的 GDDR6X 临时样品。迈向 GDDR6X 和 GDDR7 中使用的 pulse- amplitude modulation 4(PAM4)将遇到新的挑战。

Cadence 利用自身在串行链路分析PAM4 仿真方面的丰富经验,大力推动并行总线分析技术的发展。随着串行链路和并行总线领域的不断融合,Cadence 将准备好内部使用的工具,解决前沿存储器接口面临的挑战。

GDDR 接口的发展已经超越了最初的应用,即解决游戏应用中对数据饥渴型 GPU 的快速数据访问需求。如今,设计软件将 GDDR6 用于更多高性能应用,包括汽车、高性能计算、人工智能/机器学习和 5G。设计团队可以放心利用 Cadence 的全方位解决方案来应对存储器接口设计和分析方面的挑战,包括 IP、系统级芯片(SoC)、中介层、IC 封装和 PCB。

本期内容就介绍到这里啦,如果您对Cadence的信号完整性(SI) 和电源完整性(PI)工具或对Cadence其他软件产品感兴趣,欢迎随时联系我们~

|