|

我们都曾创造过本应无懈可击的设计,将其送往制造时我们感到如释重负,但某些严重违规的参数却给了我们当头棒喝。明明此前的成果已无限接近成品,我们又不得不重新回到绘图板阶段,令人沮丧的是――我们早已为此花费了数周时间。

DFM问题的影响

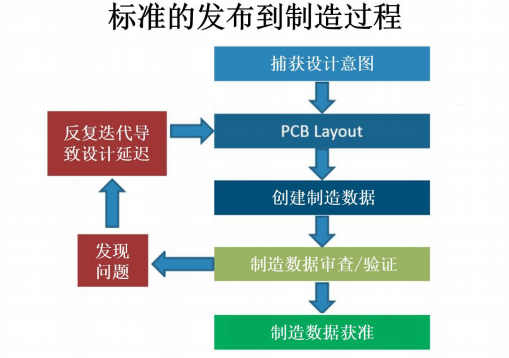

通常,大多数问题都发现得太晚了。

设计部门已经完成设计意图、布局、制造数据等阶段,正要进入审查阶段。到此阶段,一旦制造商发现电路板问题,我们将不得不回到布局过程中来解决这些问题。这可能发生多次,多次迭代后将导致设计重度延迟。最终,在我们花费了大量的时间、金钱和人力后,电路板才得以通过审查。

DFM问题太普遍了,从良率下降到未能符合上市时间安排,此类违背计划的结果在竞争激烈的市场中非常不利。我们如何打破这个循环呢?第一步是清楚认识反复困扰设计团队的常见DFM问题。明确障碍可以使我们获得更好的洞察力,从而在未来项目中实现更好的工作流程。

FM常见问题简单列举

运行DFM检查时,我们面临着许多挑战。

了解从众多PCB挑战中的哪处着手便是成功的一半。为了帮助缩小范围,我们列出了几个常见的DFM问题供您参考:

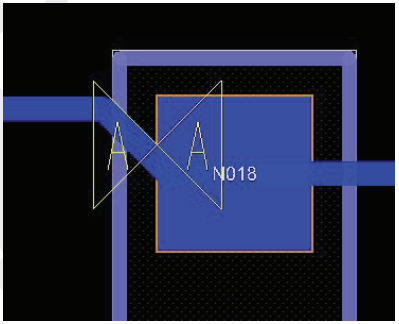

设计问题 #1(锐)角走线

问题:当焊盘与走线之间的间隙太小时,便会产生(锐)角走线,导致蚀刻剂聚集。它们是在高密度PCB上创建锐角焊盘入口时形成的。未蚀刻的铜可能使我们的电路板短路。

影响:随着时间推移,由于走线的持续侵蚀而导致的可靠性问题和最终故障。

解决方法:在设计过程将要开始时,采用增强入口布线技术,例如尽量少用45°以下走线连接,或者在该区域增加过孔以允许化学品逸出。

设计问题 #2 重复钻孔

问题:两个过孔相互重叠的点。通过目视检查计算机辅助设计(CAD)数据很难发现它们。这种情况通常在使用CAD工具时发生,此时需要产生鼠啮式不规则缺口或多个邻孔来作为槽孔。

影响:在制造层面上,钻头在钻孔操作过程中将会发生灾难性的断裂,导致项目延迟和成品之前的数据修改。

解决方法:如果我们的CAD工具有此功能,请将鼠啮和开槽操作的重复钻孔更改为槽孔类型。

设计问题 #3 丝印层与焊盘间距的违规

问题:丝印层文字或线条覆盖在铜焊盘上时即发生违规。

影响:丝印过程中产生的油墨如果没有立即清除,可能会污染焊盘。这种污染会进一步在焊接过程中导致问题。

解决方法:注意丝印层的位置,如果违规,只需将焊盘上的文字或线条移开。如果无法移开,另一种方法是将文字或线条从焊盘周围剪辑出来。

如何轻松发现错误

那么如何在设计过程中找到这些错误呢??

我们不建议尝试手动寻找。电路板设计可以有成百上千(或更多)的器件和连接,因此几乎不可能用肉眼发现所有问题。乍看之下,电路板看起来很完美,但当我们试图将它发送给制造商时,便会发现数十处错误。

无休止的归档和检查过程异常繁琐,并且随着时间的推移会在生产损失方面花

费大量成本。更好的解决办法是什么?

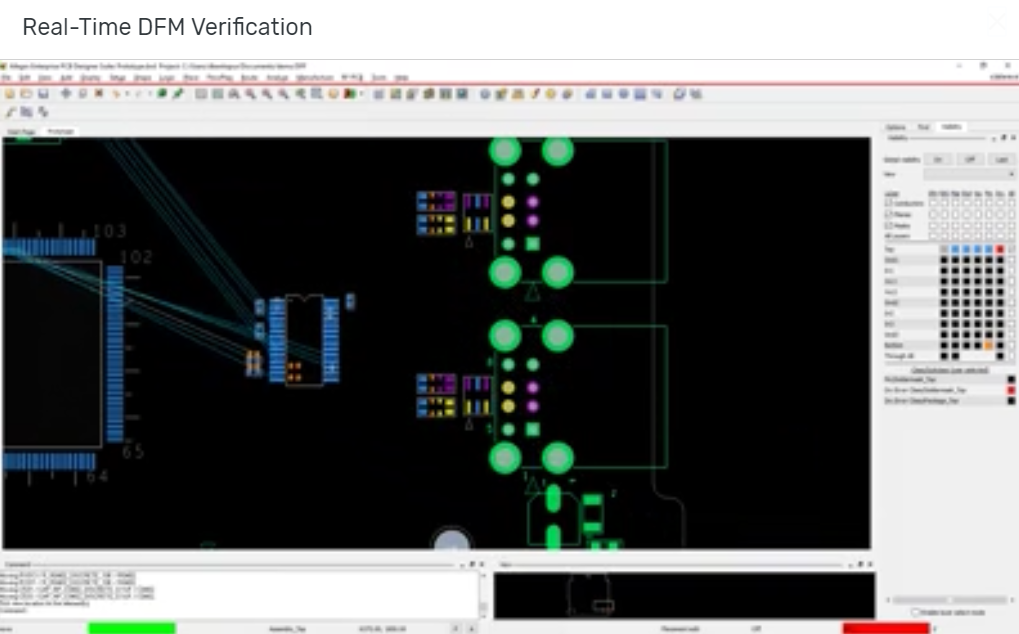

Allegro 中的实时设计--防止DFM错误发生

设计中的实时DFM检查有利于:

使用先进的Cadence Allegro® PCB DesignTrue DFM Technology软件来实现更轻松的设计。

● Key Benefits

※ 在设计时,运行设计实时制造设计规则检查,减少设计返工并缩短设计周期

※ 各种铜皮间距和铜皮面积要求规则,确保可制造性和组装质量,无需考虑电气要求

※ 易于配置、支持导入厂家约束并支持制造规则复用

※ 在设计之前,可直接在 DesignTrue DFM Program中与参与制造商合作,下载可制造性设计规则

Allegro® PCB DesignTrue DFM Technology不仅能通过实时扫描与检测电路板违规来简化设计流程,更能通过易于实施的修复手段消除多次验证迭代来大大提高生产效率。通过实时DFM检查,Allegro用户可将制造验证时间减少70%,实为简单、高效,而有效的解决方案。

简而言之,当我们一开始便按照目标规范设计时,生产力将获得极大的提高。良好的DFM将使我们的项目如期进行、防止后期变更,并保持构建成本的可预测性。如果您想了解更多关于Cadence软件的产品,欢迎随时与我们联系。

文章内容来源于:Cadence楷登PCB及封装资源中心 -资料下载 -PCB设计电子书和Cadence官网

|