|

Key Benefits

● Reduces cost and time by identifying potential problems early

● Statistical and time- and frequency-domain analysis of serial and parallel links from DC to >56GHz

● Simple block-based schematic editor to get started, supported by related Cadence tools

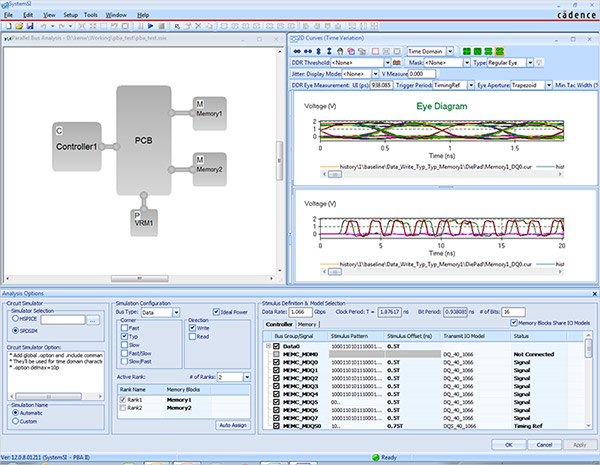

To help you quickly implement general topologies and standard interfaces, Cadence® Sigrity™ SystemSI™ technology performs automated die-to-die signal integrity analysis in two configurations: source-synchronous for parallel buses and serial links, with an emphasis on SerDes channels. Covering the range DC to over 56GHz, the SystemSI technology uses frequency domain, time domain, and statistical analysis methods. Both configurations are augmented with a general-purpose topology exploration tool.

Sigrity SystemSI brings three major features to bear to accelerate the design of your next interface.

Sigrity System Explorer

This general-purpose topology exploration tool is perfect for exploring end-to-end signal and power topologies, including letting you perform signal-integrity or transient power-integrity analysis together. Also, you can include complex interconnect models and connect them to a single driver/receiver/discreet symbol that automatically replicates the circuit for each of the ports on the interconnect model.

Sigrity SystemSI Parallel Bus Analysis

This end-to-end analysis solution targets source-synchronous parallel interfaces such as designs with DDRx memory. Pre-layout capabilities (including a via wizard) enable you to begin with models that are quickly generated and connected. As the design is refined, more detailed models can be swapped in to reflect actual hardware behavior. Concurrent simulation accounts for the effects of dielectric and conductor losses, reflections, inter-symbol interference (ISI), crosstalk, and simultaneous switching noise. These simulations are able to fully account for the effects of non-ideal power-delivery systems. Graphical outputs and post-processing options give insight for rapid system improvements.

Sigrity SystemSI Serial Link Analysis

This award-winning chip-to-chip analysis solution focuses on your high-speed SerDes designs, such as PCI Express® (PCIe®), HDMI, SFP+, Xaui, Infiniband, SAS, SATA, and USB, and makes early assessments using basic templates. Support for industry-standard IBIS AMI transmitter and receiver models let you perform simulations of channel behavior for serial links with chips from multiple suppliers. If you’re a chip model developer, you have access to techniques that assist in IBIS-AMI model development. You can add models of multiple packages, connectors, and boards to reflect the entire channel. Simulations identify crosstalk issues and show the effectiveness of chip-level clock and data recovery (CDR) techniques. Full-channel simulations including millions of bits of data confirm overall bit-error rate (BER) to determine if jitter and noise levels are within specified tolerances.

To help ease you into the environment, Sigrity SystemSI starts with a block-based schematic editor to make it easy to get started with very basic data. As design work progresses, models are swapped in to reflect the detail of design structures.

Features

● Accurate handling of non-ideal power delivery system influences on SI

● Concurrently evaluate SI effects such as losses, reflections, crosstalk, and simultaneous switching output (SSO)

● Support for industry-standard IBIS AMI transmitter and receiver models enable simulations of channel behavior for serial links with chips from multiple suppliers

● Highly automated measurement and reporting capabilities

|