|

我们介绍了在FSP中完成网络连接,接下来就需要将FSP中的设计转换成原理图,并将其生成对应的布局信息。具体流程如下:

(1)将FSP中设计的系统级布局信息生成原理图,并生成对应的原理图库。

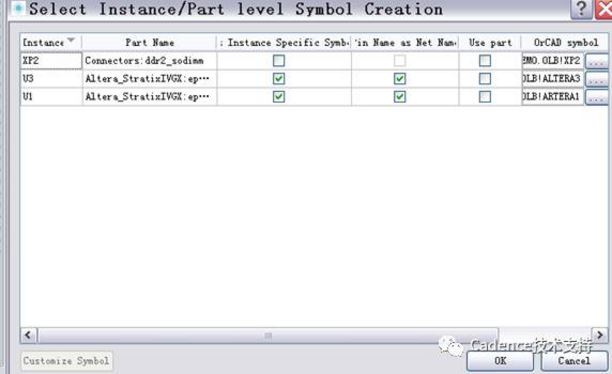

首先,执行Generate/Allegro DECIS/Setup Symbol Data,设置原理图元件库生成位置,及相应元件名,如下图:

生成元件库的位置和元件名设置

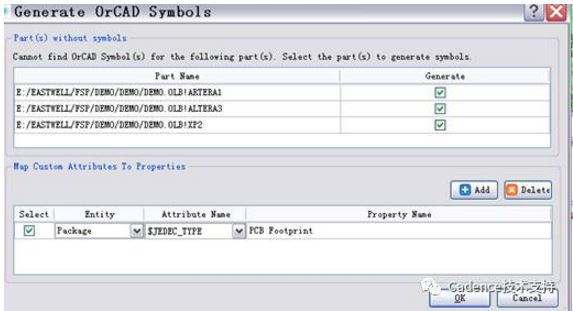

(2)执行Generate/Allegro DE CIS/Symbols,生成设计中元件库:

执行元件库生命命令

元件库创建

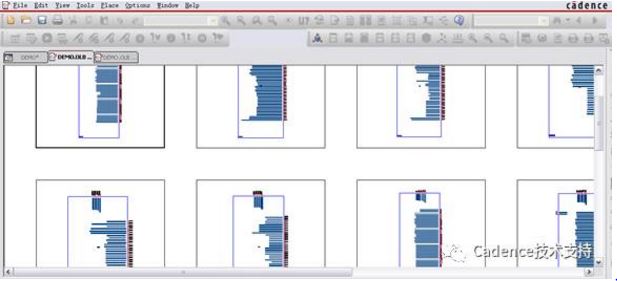

(3)完成设计的元件库创建,打开原理图库,如下图:

原理图库

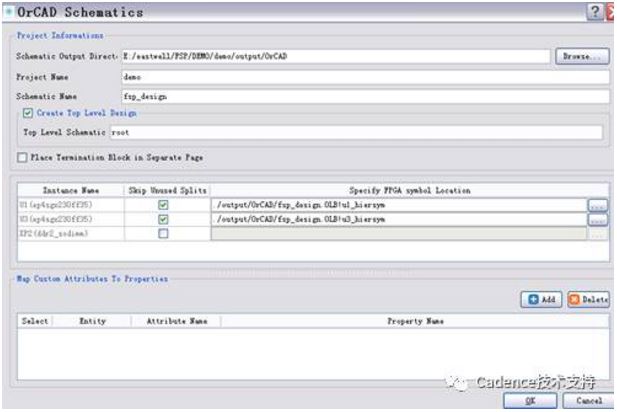

(4)完成原理图元件库的创建之后,执行Generate/Allegro DE CIS/Schematics命令,就在已经产生的原理图库基础上,创建设计对应的原理图,然后在Capture原理图中加入其它的外置元器件。

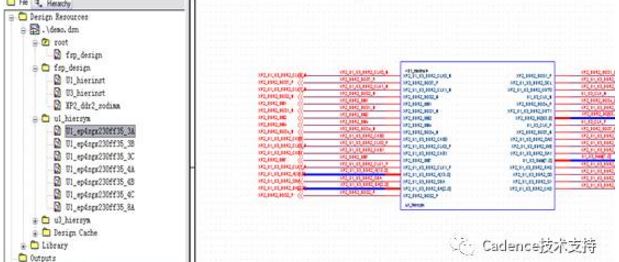

创建层次原理图相关设置

FSP生成的原理图

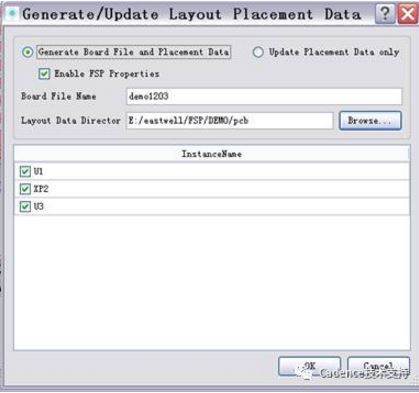

(5)生成设计的原理图后,就需要创建布局信息,执行Generate/Allegro PCBPlacement命令,创建设计布局信息。

注意:这里必须设置好BoardFile Name,而后FSP生成的布局信息中,包括这个demo1203.brd文件,这个文件将用来实现FSP与Allegro的互联集成,可以实现FSP与Allegro布局信息更新的同步。

FSP生成布局信息的设置

5、完成原理图与布局信息生成之后,接下来需要做的就是将FSP与Allegro Entry CIS、Allegro PCB紧密集成。

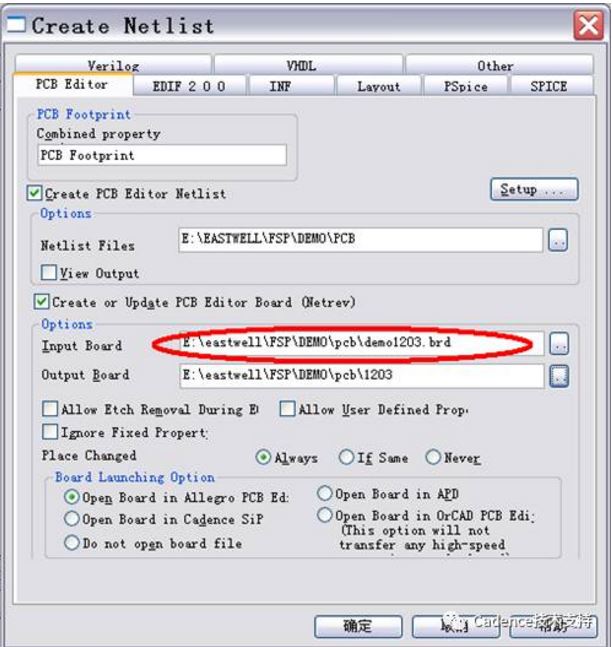

(1)将FSP生成的原理图,导出网表,导入PCB,执行Tools/Create Netlist,在Create Netlist对话框中做好导出网表的设置。

――注意:这里要与FSP集成,必须在InputBoard中选择FSP生成的布局信息中的demo1203.brd文件,这样才能将FSP的布局与Allegro中的布局集成互联,实现两者的实时布局信息更新。

原理图导出网表设置

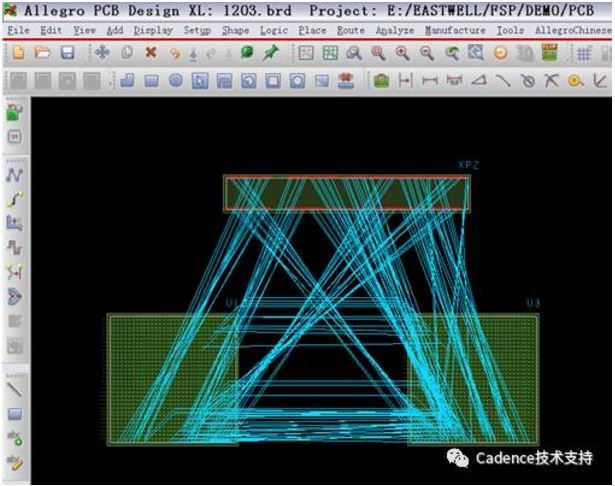

原理图导入PCB

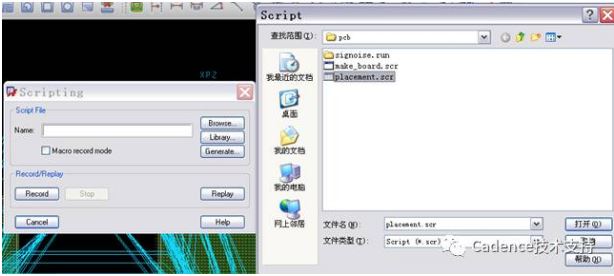

(2)在新的PCB中,执行File/Script命令,在弹出的Scripting对话框中,选择FSP设计中生成的布局相关信息中的placement.scr文件,这样FSP中所有的设计更新都会这样实时导入PCB中如下图。

PCB调用FSP布局信息placement.scr

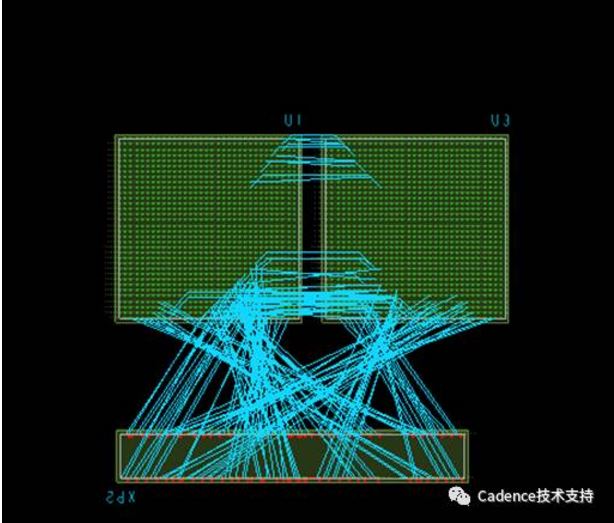

调用placement.scr布局信息之前

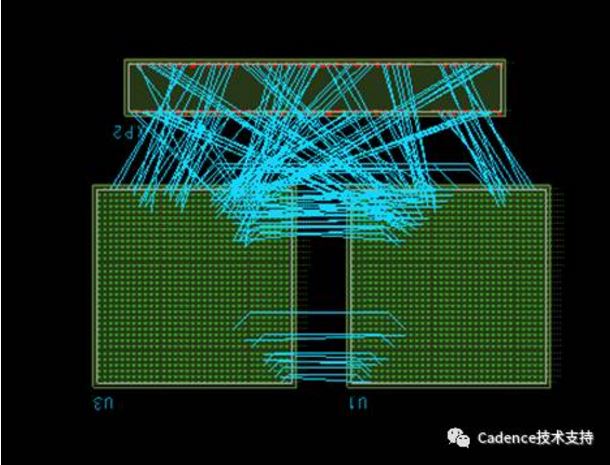

调用placement.scr布局信息之后

(3)当PCB中的布局发生变化之后,也可以实时更新到FSP设计中,在FSP中执行File/Update Placement From Board File命令,调用更新好的PCB,这样PCB的布局更新会实时调用到FSP设计中。

FSP调入PCB更新信息

Cadence Allegro FPGA System Planner提供了一个完整的、可扩展的FPGA-PCB协同设计解决方案,用户可以用它创建设计满意的引脚配置方案。它能够根据用户产品定义、接口连接、引脚配置规则(FPGA-rules)以及FPGA在PCB板上的实际布局,来进行FPGA引脚配置的综合优化。

|