|

随着集成化程度的提高,印制板设计中FPGA引脚数量越来越多,工程师设计难度越来越大,OrCAD FPGA能够应当这个挑战,包括创建初始引脚配置,与原理图紧密集成以及确保印制板硬件布线性能。Cadence OrCAD FPGA系统设计平台提供了一套完整的、可扩展的FPGA-PCB协同式设计解决方案,以用于板级的FPGA设计,它能够自动对引脚配置进行“硬件-规则-精确”的优化。

Cadence OrCAD FPGA取代了引脚手动配置方式,综合容易出错的自动配置方式,形成了独特的布局解决方案,减少了不必要的设计迭代,减少了创建较优化引脚配置方案的时间,提高了设计效率。 Cadence OrCAD FPGA System Planner提供了一个完整的、可扩展的FPGA-PCB协同设计解决方案,用户可以用它创建设计即正确的较佳引脚配置方案。它能够根据用户产品定义、接口连接、引脚配置规则(FPGA-rules)以及FPGA在PCB板上的实际布局,来进行FPGA引脚配置的综合优化。通过自动综合优化引脚配置,用户不仅减少了FPGA布局的初始引脚配置时间,还避免了设计错误的发生。这种独特的引脚配置方法,消除了手工设计方法中固有的不必要的物理设计迭代。

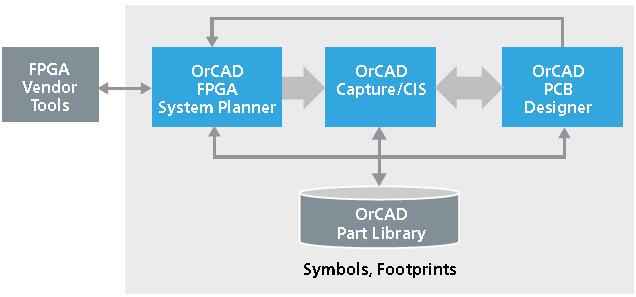

OrCAD FPGA System Planner设计平台集成了OrCAD Capture和OrCAD PCB Editor设计模块,可以直接读取和创建Capture原理图和符号文件,并支持OrCAD PCB Editor的封装库。如果在PCB板级设计中需要调整布局,OrCAD FPGA System Planner设计平台可以在引脚优化后,将数据直接传递给OrCAD PCB Editor。

优点

1、可扩展、高性价比的FPGA-PCB协同设计解决方案;

2、加速PCB设计流程,能够用较短的时间优化引脚配置;

3、加速FPGA与PCB设计之间的设计集成;

4、减少由于FPGA引脚配置不当引起的反复设计迭代;

5、通过引脚配置优化,优化PCB设计,减少设计层数;

6、减少PCB板层设计进程中不必要的设计迭代。

功能特性

OrCAD FPGA System Planner设计技术

FPGA系统是PCB设计的一个子系统,包括一个或多个与FPGA相连的FPGA和非FPGA元件。

传统的引脚配置方法是典型的手工方法,通常都是基于一个表格来进行的。这些传统的手工设计工具要求用户在不考虑其它元件布局,不考虑接口、信号的可布线性能的情况下,进行引脚配置。首先,这些工具没有在线的实时规则检查,用户不能确保信号被正确配置给FPGA引脚。这样设计的结果就是,用户必须在这些基于表格的设计工具与FPGA第三方设计工具之间作若干次迭代设计后,才能找到合适的引脚配置。

这些决定了PCB板层设计师和FPGA设计师之间大量的设计迭代,因为前者不能在可用的PCB板层对FPGA进行准确的信号布线,而后者不得不接受PCB板层设计师纸面和口头上建议的引脚配置。这样的情况下,一旦FPGA设计师修改引脚配置,那么所有的硬件设计师都必须修改原理图设计,才能进行进一步的PCB设计,如此反复的设计迭代增加了许多工作量,并且可能会降低团队成员的工作积极性。此外,由于这是一项手工配置进程,设计中的错误很难被发现,这可能导致物理样机的失败,增加物理设计迭代。

虽然这些工具可以自动综合各方面的修改,包括FPGA设计师、硬件设计师、PCB板层设计师的设计修改,但是它并不能解决这些设计迭代的根源问题。因为引脚配置不仅由以下三点决定――FPGA资源可用性、FPGA生产商提供的引脚配置规则和印制电路板FPGA引脚可布线性能,它还需要在设计末端进行许多迭代,从而延迟了如今复杂的、拥有多个多引脚FPGA印制板的设计周期。

典型设计构思

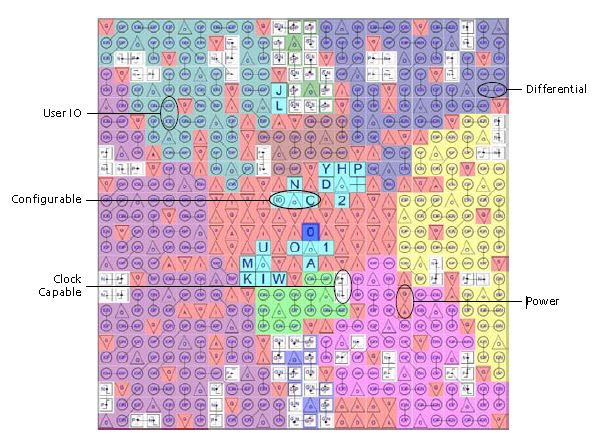

OrCAD FPGA System Planner 中包含一个FPGA硬件库,可以用来协助硬件布局。它使用OrCAD PCB Editor的元件封装来创建平面视图设计,并允许用户快速创建FPGA系统元件的相对位置。此外,它还允许用户指定FPGA子系统中元件之间的高端接口定义,包括DDR2、DDR3和PCI等接口定义,用户可以用这些接口来实现FPGA 与DIMM组件之间或者两个FPGA之间的互连特性。OrCAD FPGA System Planner 还能够定义差分对信号、电源信号和时钟信号。

FPGA硬件规则

OrCAD FPGA System Planner自带一个精确的FPGA模型库,它包括FPGA硬件生产商所确定的引脚配置规则和特殊电气规则。 这些FPGA模型通过合成引擎确保FPGA生产商定义的电气规则正在有效执行。这些电气规则,诸如时钟与时钟区域选择、库配置、同步交换预定、缓冲驱动使用以及I/O标准参考电压设定等等。在系统合成过程中,OrCAD FPGA System Planner可以自动检查数以百计的规则组合,用以确保FPGA引脚配置的优化。

优化引脚配置

OrCAD FPGA System Planner提供一种基于OrCAD PCB封装的设计方式,用以创建FPGA系统的布局视图。用户可以通过DDRx、PCI、SATA、前端总线等接口来指定系统中完成布局的元件与FPGA之间的高端互连关系,它可以用来实现系统中的FPGA与其它元件互连性能,减少FPGA系统设计构思的时间。

一旦确定子系统中FPGA与其它元件连接关系,OrCAD FPGA System Planner就能够立即按照用户的设计构思,将系统引脚配置、可用FPGA资源、FPGA外围元件布局和FPGA生产商的引脚配置规则等进行有效整合。

OrCAD FPGA System Planner内置一个DRC引擎,可将FPGA生产商提供的引脚配置规则、参考电压规则和终端规则进行有效整合。这种基于规则的合成引擎,可以有效避免多个FPGA连接时PCB物理设计中的反复迭代。引脚配置算法得到优化,可以为一组引脚配置脚佳的接口信号,从而能够尽量减少设计中的交叉网络,提高PCB的布线性能。

与Cadence设计创建紧密集成

OrCAD FPGA System Planner设计平台集成了OrCAD Capture平台,便于创建FPGA子系统原理图,它可以调用OrCAD Capture元件库中自带的FPGA符号进行原理图设计。如果用户需要,OrCAD FPGA System Planner还可以创建基于互连特性的FPGA分裂元件,或者一个分裂符号。

与FPGA第三方工具紧密集成

OrCAD FPGA System Planner不仅与OrCAD PCB设计工具紧密集成,还能够与FPGA设计工具实现无缝链接。它可以直接输入和输出FPGA生产商的引脚配置规则文件,这种性能使得FPGA设计师在设计阶段就能够对FPGA引脚功能配置进行准确评估。FPGA设计师根据要求做出的任何设计修改,都可以直接输入OrCAD FPGA System Planner工具,能够确保整个设计中引脚功能配置保持一致。

布线前引脚配置优化

初始引脚配置,决定了电路板上FPGA的布局布线性能,然而,减少FPGA设计师、PCB板层设计师、硬件设计师之间的成本设计迭代还有个很长的过程。一旦PCB板层设计师开始规划FPGA相关的接口和信号走线,基于FPGA的走线构思、板层规则和扇出方式的考虑,FPGA引脚配置有可能还需要进一步的优化。OrCAD FPGA System Planner当然也考虑到了这一点,它为用户提供了一种优秀的引脚配置的优化方式,可以实现布局后配置优化,以及FPGA接口、信号线布线期间的配置优化。

可扩展性

OrCAD FPGA System Planner具备设计扩展性,可以随着设计复杂度的提高,提升至Allegro FPGA System Planner:

1、ASIC FPGA System Planner产品模块――提供一次无限制FPGA的综合管脚配置与优化;

2、4 FPGA System Planner 产品模块――提供一次最多4个FGPA的综合与管脚优化设计;

3、2 FPGA System Planner――提供一次最多2个FGPA并行管脚配置、综合和后端布局优化设计;

4、FPGA System Planner L――提供1个FPGA的综合和后端布局优化设计。

|