|

复杂的物理和电气规则,高密度的元器件布局,以及更高的高速技术要求,这一切都增加了当今PCB设计的复杂性。不管是在设计过程的哪一个阶段,设计师都需要能够轻松地定义、管理和确认简单的物理/间距规则,以及至关重要的高速信号;同时,他们还要确保最终的PCB满足传统制造以及测试规格所能达到的性能目标。

系统公司受半导体行业所提供新设备和设计方法学的影响,通常会面临更多挑战,比如越来越小球栅阵列封装(BGAs)的管脚间距和越来越多的管脚数量。此外,新设备还会使用不断更新的标准化接口,例如DDR3、DDR4、PCIExpressGen3、USB3.0等等,需要学习新的方法,才能将它们在PCB板上实现。在技术复杂性提高的同时,企业还希望使自己的产品实现差异化、产品上市时间更快,产品价格更低、功能更多、且最终产品尺寸更小。因此,许多企业现在都将业务外包到成本较低的地区、或与当地的企业合作。为应对越来越高的复杂性,PCB设计师需要能为他们解决技术难题和设计方法学难题的解决方案。

Cadence Allegro PCB Designer 设计解决方案

Allegro PCB设计解决方案能为解决与实现高难度的、与制造密切相关的设计提供完整的设计环境。该设计解决方案集成了从设计构想至最终产品所需要的一切设计流程,包含设计输入、元件库工具、PCB编辑器和一个自动/交互连布线器,以及用于制造和机械CAD的接口。并且随着设计难度和复杂性的增加,可通过统一的数据库架构、使用模型和库为Cadence OrCAD和Allegro产品线提供完全可升级的PCB解决方案,加速你的设计速度并扩大设计规模。从而提高了设计效率,缩短了设计周期,以及更快地实现量产。

优点

❁可靠、可升级、可节约成本的PCB编辑和布线解决方案,并随设计的需求而时刻更新。

❁提供从基础/高级布局和布线到战略性规划和全局布线的完整的互联环境。

❁通过约束驱动式PCB设计流程避免不必要的重复

❁支持以下各种规则:物理、间距、制造、装配和测试的设计(DFx)、高密度互连(HDI)、及电气约束(高速)

❁包含一个从前端到后端的约束管理系统,用于约束创建与管理。

❁具有通用和统一的约束管理系统,用于创建、管理和验证从前端到后端的约束。

❁兼容第三方应用程序的开放式环境,提高效率的同时,提供访问其他品种工具的入口。

PCB Editor技术

约束驱动PCB设计环境

Allegro PCB Designer的核心是PCB编辑器,它是一个直观易用的约束驱动式环境,用于创建和编辑从简单到复杂的PCB。它具有众多特性,可解决广泛的设计和可制造性难题:

• 强大的平面规划和布局工具,包括布局复制功能,加速布局设计

• 强大的基于形状的推挤、紧贴交互式编辑,在建立高效互连设计环境的同时,还能实时、提醒式显示长度和时序余量

• 动态覆铜能力可在布局和布线反复过程中提供实时铜皮避让功能和自动恢复功能

此外,Allegro PCB编辑器还能生成一整套光绘、裸板制造和测试输出数据,包括Gerber274x、NCdrill及各种形式的裸板测试数据。

约束管理

约束管理系统实时地显示了物理/间距和高速规则以及它们的状态(根据设计当前所处的状态),并且可适用于设计过程的任一阶段。每个工作表提供了一个电子数据表界面,能够让用户以层级的方式进行定义、管理和确认不同的规则。这种强大的功能应用可以让设计师用图形创建、编辑和评估约束集,使其作为图形的拓扑结构,当作理想的实现策略的电子蓝图。一旦约束被提交到数据库中,它们就可被用来驱动信号线的放置和布线过程。该约束管理系统是完全集成到PCB编辑器中,而约束可以随着设计过程的进行而被实时地确认。确认过程的结果是用图形化的方式表示约束条件是否满足,满足约束用绿色显示,不满足约束就用红色显示。这可使设计师可以及时地看到设计的进度,以及因电子数据表中任何设计变动而产生的影响。

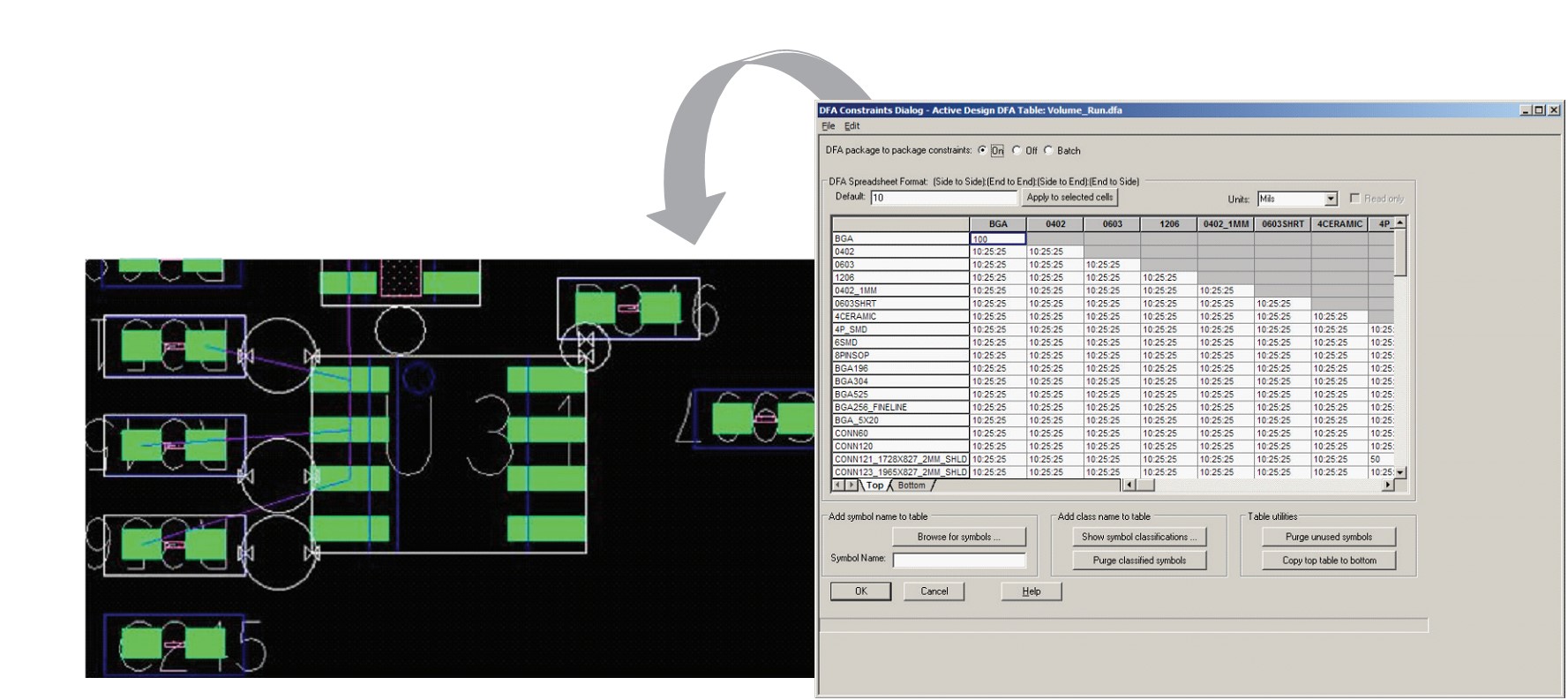

PCB设计规划与布局

约束和规则驱动的方法有利于强大而灵活的布局功能,包括互动和自动的元件布局。工程师或设计师可以在设计输入或布图规划阶段将元件或支电路分配到特定的“区域”。可以通过REF、封装方式、相关信号名、零件号码或原理图表/页面号码来过滤或选择元件。当今的电路板上有成千上万种元器件,需要精确的管理,通过实时的器件装配分析和反馈,得以实现器件装配时从整体上来考虑并满足EMS规则,以提高设计师的设计速度和效率。DFA(可装配型设计)分析,实现了在互动式元件放置时,实时地进行DFA规则检查。基于一个器件类型和封装排列的二维电子表格,DFA可以实时地检查器件的边到边、边到端或端到端的距离是否违反较小要求,使得PCB设计师可以同步地放置元器件以实现较优的可布线性、可生产性和信号时序。

布局复制技术

Allegro PCB Designer中出色的布局复制技术使用户能够在设计中快速布局布线多个相似的电路。它使用户能够使用一个可用于设计内其他实例的已布局布线电路实例作为模板。已保存布局模板还可用于使用相似电路的其他设计。复制布局时,用户可以从顶层到底层翻转或镜像电路。当电路被从顶层移动到底层时,所有相关布线层,包括埋盲孔,都会被映射到正确的层。

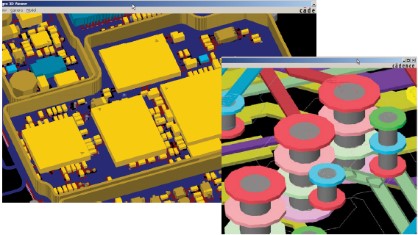

PCB显示与可视化

所有PCB Editor产品均内置三维查看器。该三维环境支持数个过滤选项、相机视图、实心、透明、线框等图形显示选项,以及用于平移、缩放和旋转显示内容的鼠标驱动式控件。三维视图还支持复杂孔结构或电路板绝缘层部分的显示。使用命令行可打开多个显示窗口,并且可以捕获三维图像并保存成JPEG格式。翻转电路板功能将设计围绕其Y轴“ 翻转”,在线路板中翻转设计数据库。这种“翻转”重新组织设计的显示方式,使原来的从顶部至底部显示变为从底部至顶部。对于在实验室调试电路板的硬件工程师、或制造车间的装配/测试工程师来说,从CAD系统内部有一个真正的底侧视图是非常重要的。翻转电路板不仅限于查看用途,处于该模式时还能进行设计编辑。

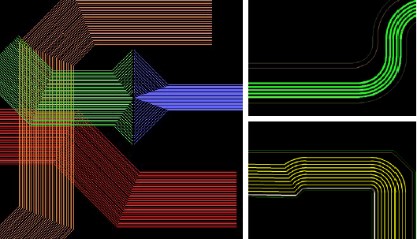

交互式走线编辑

PCB编辑器的布线功能提供的强大、交互式的功能,在提供较大化布线效率的同时保持用户对全局的控制。实时的基于形状的、任何角度的推挤布线使用户可以在“推挤优先”、hug-preferred、或hug-only等模式间选择。

在布线过程中,设计师可实时、图形化地查看对于具有高速约束的互连,还剩下多少时序裕量。交互式布线还能对具有高速长度或延迟约束的网络,实现多条网络的成组布线及交互式微调。

多线路布线

多线路布线允许用户将多条线路作为PCB上的一组快速布线。配合“紧贴轮廓”选项,该工具能帮助设计师在刚性―柔性设计的柔性部分上面布置多条线路,时间仅需数分钟而不像传统的一次一条布线的方式需要数小时来完成。紧贴轮廓选项确保布线时可以紧贴柔性设计部分的轮廓曲线。

PCB制造

Allegro能生成一整套光绘、裸板制造和测试数据,包括:Gerber 274x,NC drill及各种形式的裸板测试数据。更重要的是,通过支持ODB++/IPC 2581等数据接口,Cadence支持业界朝向无Gerber制造的趋势方向发展――ODB++/IPC等数据格式可以创建精确可靠的制造数据,从而实现高品质的无Gerber制造。

这就让缩短设计周期时间的相关问题变得更加复杂。手动操作解决多用户问题非常耗时、缓慢而且易于出错。

Highspeed高速设计

对DDR3、DDR4、PCIExpress、 USB3.0等标准化高速接口越来越多的使用,带来了一整套的实现PCB时必须遵守的约束规则。

通过Highspeed高速设计模块,Allegro PCB Designer可以快速、自动的遵守并实现高速接口的约束条件。

高速设计功能提供多方面的电气规则,确保PCB设计符合高速接口的规范。此外,它开可以使用公式(Formulas)和扩展约束规则。

小型化设计

约束驱动式HDI设计流程

随着BGA管脚间距减少至1mm―0.8mm以下,或低于0.65或0.5mm管脚间距――用户被迫使用通过高密度互连(HDI)来实现的一种表面积层PCB技术。

虽然小型化在许多细分市场未必是首要目标,但向表面积层技术的转型对扇出BGA却是必要的――特别是当它在每一侧都有三至四排管脚的时候。

Allegro PCB Designer可通过其小型化选件提供经验证的约束驱动式HDI设计流程及一套全面的设计规则,可被应用于各种类型的HDI设计,从厚模的bulidup层/核心的组合到完全的Build-up技术流程,例如任意层过孔技术(ALIVH)。

此外,它还包含自动添加HDI的功能,可缩短创建一个正确结构的设计的时间。

埋入式元件

缩减最终产品尺寸可通过许多不同的途径来完成。PCB设计师目前采取的一种方法是将已封装元件埋入内部各层。Allegro PCB Designer通过其小型化选件提供约束驱动式嵌入式元件布局和布线。它支持传统的直接安装,也支持新的间接安装方法。此外,它还能创建和管理各层上指定给嵌入式元件的腔体。

总线设计规划与布线

受总线互连支配的高度约束、高密度的设计可能需要花费大量时间才能完成策略规划和布线。再加上当今元件的密度问题、新的信号等级、以及特定拓扑要求――也难怪传统CAD工具技术难以捕获设计师的特定布线意图并遵守意图。Global Route Environment提供捕获并遵守设计师意图的技术和方法学。通过内部互连规划架构和全局布线引擎,用户第一次便能够自然地将经验和意图输入理解他们意图的工具。

用户可以抽取互连数据(通过内部互连规划架构),并快速收敛至一个解决方案,并使用全局布线引擎使其生效。互连抽取减少了系统必须处理的元件的数量――从可能的数万个减少到几百个――从而大幅减少了必须的手动操作。

使用抽取数据,通过提供数据和用户设计意图相关的开放区域的可视化/空间图,可加速规划和布线过程。此时布线引擎可处理布线细节,遵守既定意图,而用户无需立即可视化并处理互连问题。对当前设计工具的大幅简化,意味着用户收敛到成功互连解决方案的过程可以比以前快得多和容易得多,通过提升效率来缩短设计周期。

模拟/RF设计

Allegro PCB Designer通过其Analog/RF设计选件,可提供混合信号设计环境,从原理图到PCB设计,带反标功能,经过验证可增加高达50%的设计效率。它允许工程师在Allegro PCB 设计环境中创建、整合并用数字/模拟电路更新模拟/RF/微波电路。通过丰富的PCB设计功能和强大的与RF模拟工具的接口,它允许工程师从Allegro Design Authoring、Allegro PCB Designer或Agilent ADS启动RF设计。

团队协同设计

全球分布的设计团队越来越多,使缩短设计周期的难题雪上加霜。人工处理多用户问题的权宜措施非常耗时、缓慢并且容易出错。

Allegro Team Design团队设计技术提供一种多用户、并行式设计方法学,可加快上市时间、缩短版图时间。无论团队地理距离的远近,并行工作于一个版图的多个设计师均可访问同一数据库。设计师可以将设计分为几个部分或区域,可以由设计团队的几个成员进行布线和编辑。设计既可通过软边界进行垂直分割(部分),也可以水平分割(层) 。从而使各设计师均能看到所有划分的部分,并更新设计视图,监控其他用户部分的状态和进度。这种分割能大幅缩短整体设计周期并加速设计过程。

PCB AutoRouter技术

Allegro交互式自动布线技术(AiDT/AiPT等)与PCB编辑器紧密集成。通过PCB Router接口,所有设计信息和约束都自动从PCB编辑器传出。布线一旦完成,所有布线信息又自动传回PCB编辑器。

设计复杂性、密度的增加和高速布线约束使人工PCB布线变得困难和耗时。复杂布线中已有的困难通过强大、自动化的技术得到了较好的解决。该强健的、经过实际验证的自动布线器包含批量布线模式,它有广泛的用户自定义布线策略控制,以及内置式自动化策略功能。

DFM规则驱动式自动布线

Allegro PCB的可制造性设计功能可以大幅提高制造成品率。制造算法提供散布功能,以基于可用空间的方式自动增加导体间隙。通过重新放置导体,在导体和管脚、导体和SMD盘、以及相邻导体间产生额外空间,实现导体自动散布,帮助提高可制造性。用户在定义一系列间距值、或使用默认值方面具有一定灵活性。

高速约束驱动式自动布线

高速布线约束和算法可处理差分对、网络拓扑规划、时序、串扰、布线层指定、以及当今高速电路所需的特殊要求。自动布线算法可智能地处理孔周围或通过孔的布线,并自动遵守预定长度或时序条件。自动网络屏蔽用于减少对噪声敏感的网络上面的噪声。不同的设计规则可能应用到不同的设计区域;例如,用户可以在设计的互连区域指定严格的间距要求,而在其他地方指定不太严格的规则。

操作系统支持

Allegro平台技术:

• Sun Solaris

• Linux

• IBM AIX

• Windows

OrCAD平台技术:

• Windows

|