常见信号完整性问题及解决方法

1 、常见信号完整性问题

信号完整性(Signal Integrity)是指信号未受到损伤的一种状态,它表示信号质量和信号传输后仍保持正确的功能特性。常见的SI问题包括反射、串扰、延迟、振铃、地弹、开关噪声、电源反弹、衰减等,解决信号完整性问题的关键在于对互连线阻抗的认识,很多SI问题都与互连阻抗有关,下文将从互连线阻抗的角度描述反射、串扰、定时问题。

2 、反射

反射问题反映的是由单个网络的信号质量,与单个网络的信号路径及信号返回路径的物理特性有关。信号沿单个网络传播时,感受到互连线的瞬态阻抗变化引致互连阻抗发生变化的主要因素有线宽变化、层转换、返回平面间隙、接插件、分支线、T型线或桩线、网络末端。

3 、串扰

串扰发生在两个相邻的网络之间,若一个网络发生动态变化,将会通过场的作用将噪声耦合到与其相邻的静态网络上,从而影响其信号质量。信号传播时的信号路径与返回路径存在边缘场,当一个网络发生动态变化时,通过边缘场的作用,容性、感性耦合电流对相邻网络造成影响。开关噪声、地弹都是由串扰引起的。

4 、定时

集成电路只能按规定的时序接收数据,过长的信号延迟可能导致时序违背和功能混乱。当系统时钟很高时,信号在器件间的传输时间以及同步准备时间都缩短了,驱动过载、走线过长都会引起延时。常见的时序系统分为普通时序系统和源同步时序系统2类。

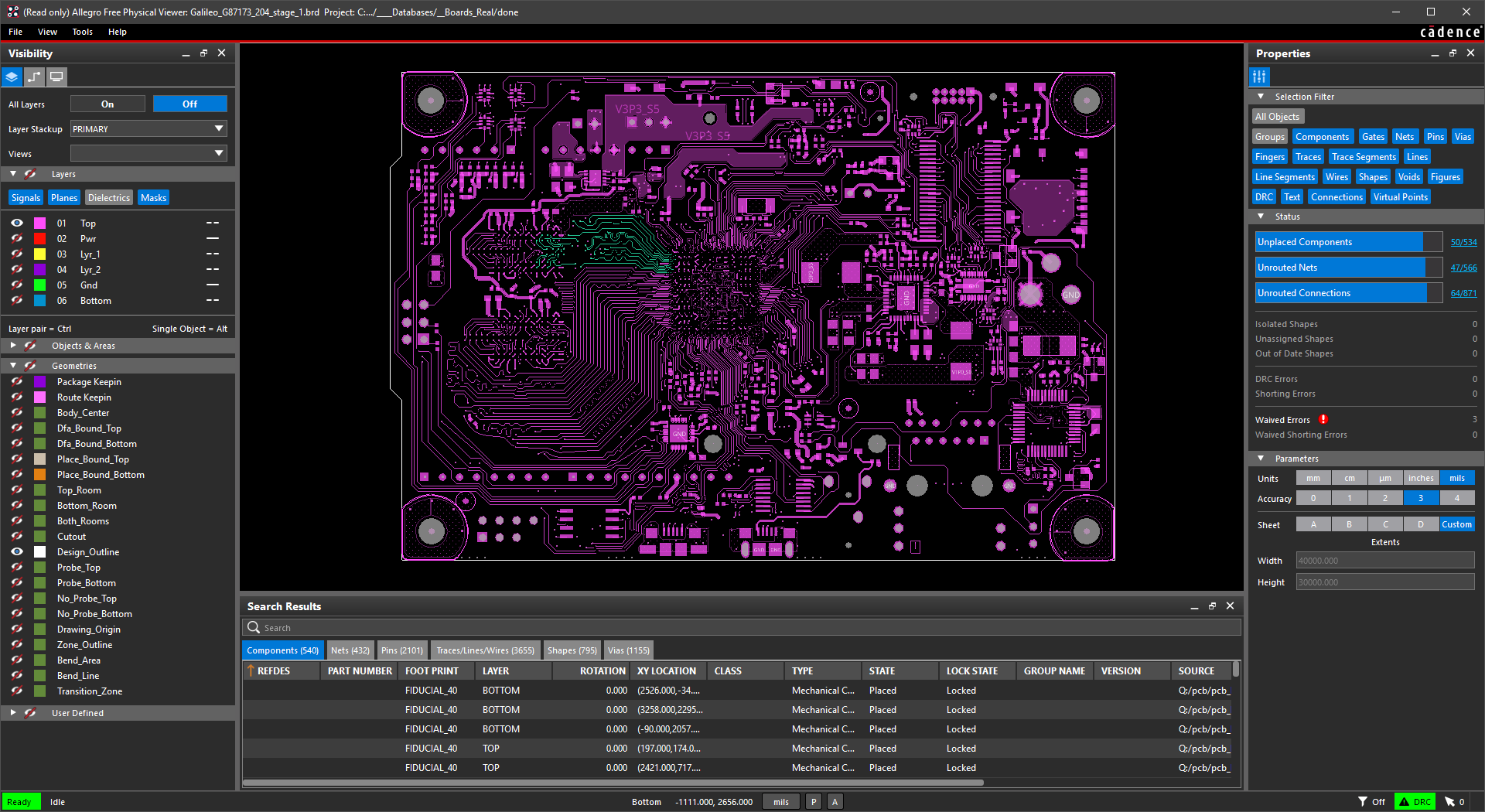

Allegro SI是Cadence公司为了满足高速系统和板级设计需要而开发的工程设计环境。它将功能设计和物理实际设计有机的结合在一起。设计工程师能在直观的环境中探索并解决与系统功能息息相关的高速设计问题。在进行实际的布局和布线之前,Allegro SI Interconnect Designer使设计工程师在时间特性,信号完整性,EMI,散热及其他相关问题上作出较优化的设计。这种统一的考虑不仅在单块板的系统中得到完美体现,更能在多块板构成的系统中,包括ASIC芯片,电路板,连接电缆,插接件等之间的连接进行分析。

在Allegro SI的参数设置环境中你可以针对不同pcb设计要求规定不同的约束条件。这些不同的约束条件可以通过参数分配表分配给电路板上不同的特定区域,或者分配给某一个信号组(group),甚至具体到某一个网络。这些约束条件包括了范围广泛的物理和电气性能参数,如常见的PCB线宽,过孔数目,阻抗范围、阻抗匹配等。

Allegro SI内部包括SigNoise信号完整性分析工具,SigNoise能接受IBIS,Elecmodel和Quad模型,转换成其独特的设计模型化语言(DML)以完成复杂I/O结构的建模。