|

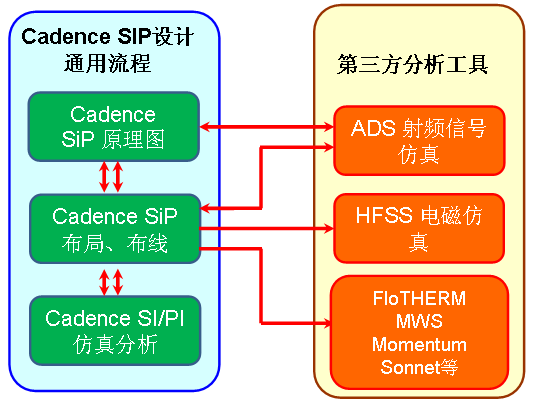

CADENCE-SiP为系统设计及封装设计软件, 它不仅提供从前端原理图到后端SiP封装的物理实现,同时提供各种第三方的验证工具接口,从而具备一套完整的小型化封装设计的解决方案.

1. Cadence SIP多芯片堆叠技术带给硬件产品小型化以质的飞跃

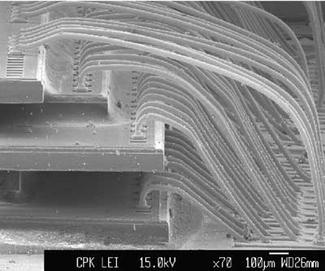

SiP技术所特有的三维芯片堆叠和埋入式器件极大的缩小了封装的外形尺寸。

从设计的角度讲,SiP设计引入从性能上允许的器件和布线的高度密集, 由于综合了键合工艺、倒装芯片工艺、堆叠芯片工艺、嵌入组件工艺、MEMS集成和封装堆叠工艺等众多拓扑形式,这使得设计师可以使用SiP实现一个小型化的完整的系统。

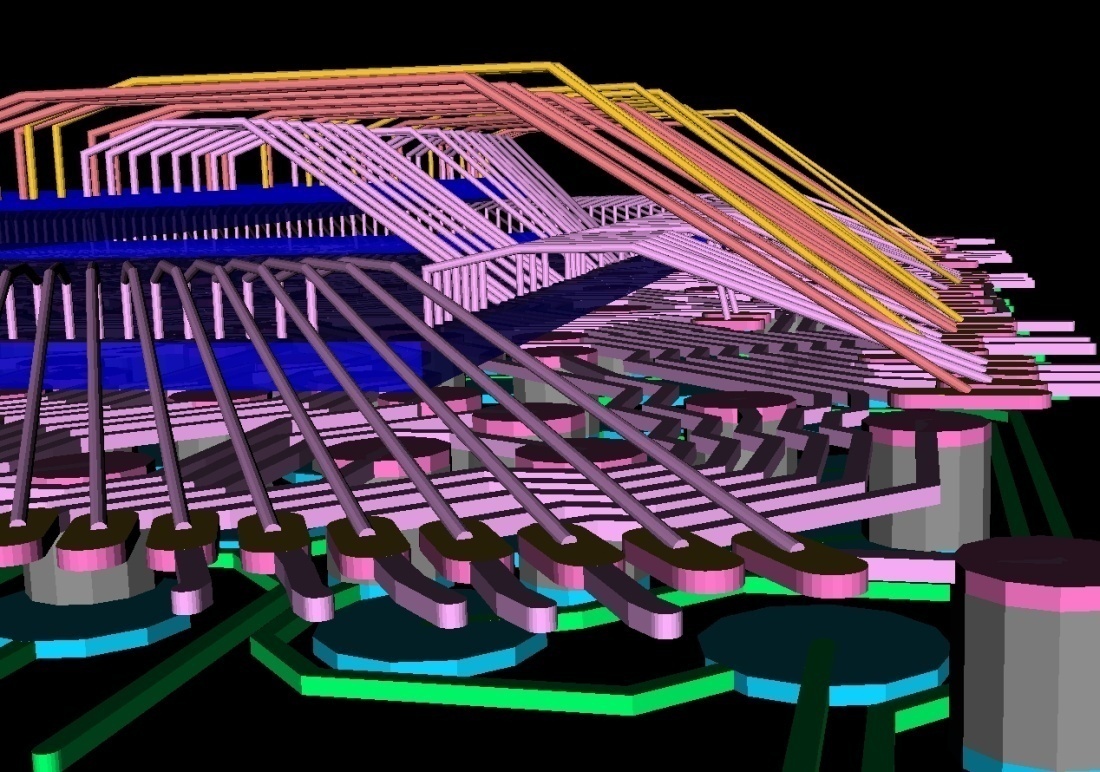

封装设计效果 封装实物图

特色

1) 降低PCB的费用――更少的层,更少的封装材料

2) 产品性能的提升30-50%――缩短互连 (更少的寄生参数,更少的延时)

3) 面积缩小80%以上

4) 功耗的降低30-50%――传输路径短,消耗的电能相对降低

5) 减少噪声 (EMI)――传输路径短,对外产生的干扰也相对减小

6) 成熟产品模块化――将成熟的产品模块化,产品化有利于提升设计质量及产品可靠

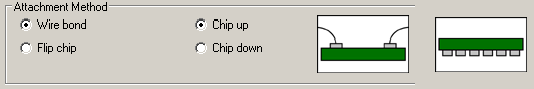

2. 多种连接方式与灵活封装形式的支持

1) 支持多种封装工艺如:金丝压焊、周边阵列倒装芯片、全阵列倒装芯片,以及堆栈式多硅芯片封装。

2) 支持多种组建连接方式:WireBond、Flip-Chip等组件连接方式

3) 灵活支持RF电路和高速数字电路兼容于同一封装

4) 支持直接借用PCB设计文档,在PCB设计的基础上增加SIP设计

3. 强大的布线能力

1) Cadence-SiP完美继承了Allegro PCB软件的强大布线功能,可以全自动的完成复杂的布线要求,成熟的技术,庞大的用户群,与Allegro相仿的操作界面,有利于设计人员的培训和快速上手。

2) 支持多种模块复用方式

3) Bonding线的灵活扇出方式:

4. 规则驱动设计方法是Cadence 的传统优势

约束驱动作为PCB版图设计的灵魂,在SiP设计中也得到了充分的体现。越来越复杂的衬底设计是传统CAD工具和布线工具难以完成的,Cadence-SiP从原理图开始就嵌入了约束管理器器,可以方便的定义衬底布局布线的约束要求,诸如线宽、间距、线路阻抗、传输延时、差分线、阻抗匹配等的设定,针对衬底上的RF信号和高速数字信号时钟,Cadence-SiP的约束驱动功能可以有效的保证时序的正确性。

功能特色

1) 实时监控Bouding线的状态

2) 实时监控布线是否满足规则设置,绿色标尺表示满足规则约束。

3) 实时监控布局是否满足DFM工艺规则,当违反规则时用出现DRC标识。

5. 封装设计3D查看与验证

为了提高功能密度,SiP设计在封装内采用了复杂的三维(3D)架构。包括堆叠金属线压焊裸片、堆叠在倒装芯片裸片上的金属线压焊裸片、裸片之间直接连BONDING线、使用媒介基板、以及包括堆叠封装(PoP)在内的其它复杂组合。

功能特色

1) 3D堆叠方式预览很好的帮助设计师或制造商理解层叠的堆叠方式。

2) 支持完整个设计预览或特定对象预览,例如晶粒堆栈或复杂的导孔阵列。

3) 辅助检查DFM问题,验证产品的可靠性,从而设计问题,DFM工艺问题发现在设计前端。

6. Cadence

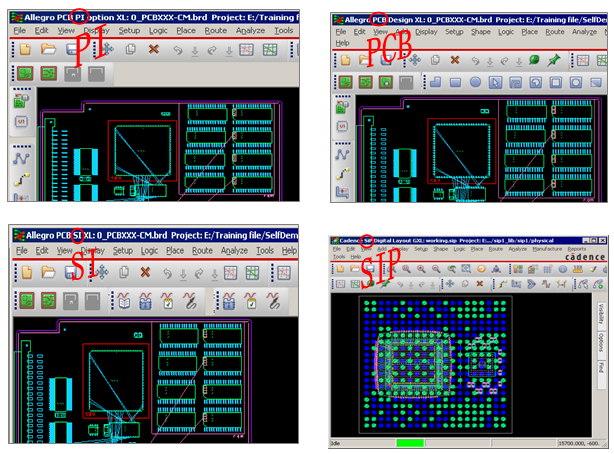

SIP、PCB、SI/PI等设计与分析软件统一底层数据、统一用户界面

1) 从方案设计到仿真分析的各个环节,统一的底层数据

2) 设计界面到仿真界面保持一致

3) 避免数据导入导出,降低设计错误

4) 界面风格统一,学习成本低,学习一个工具等于学会多个工具

|